Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 29

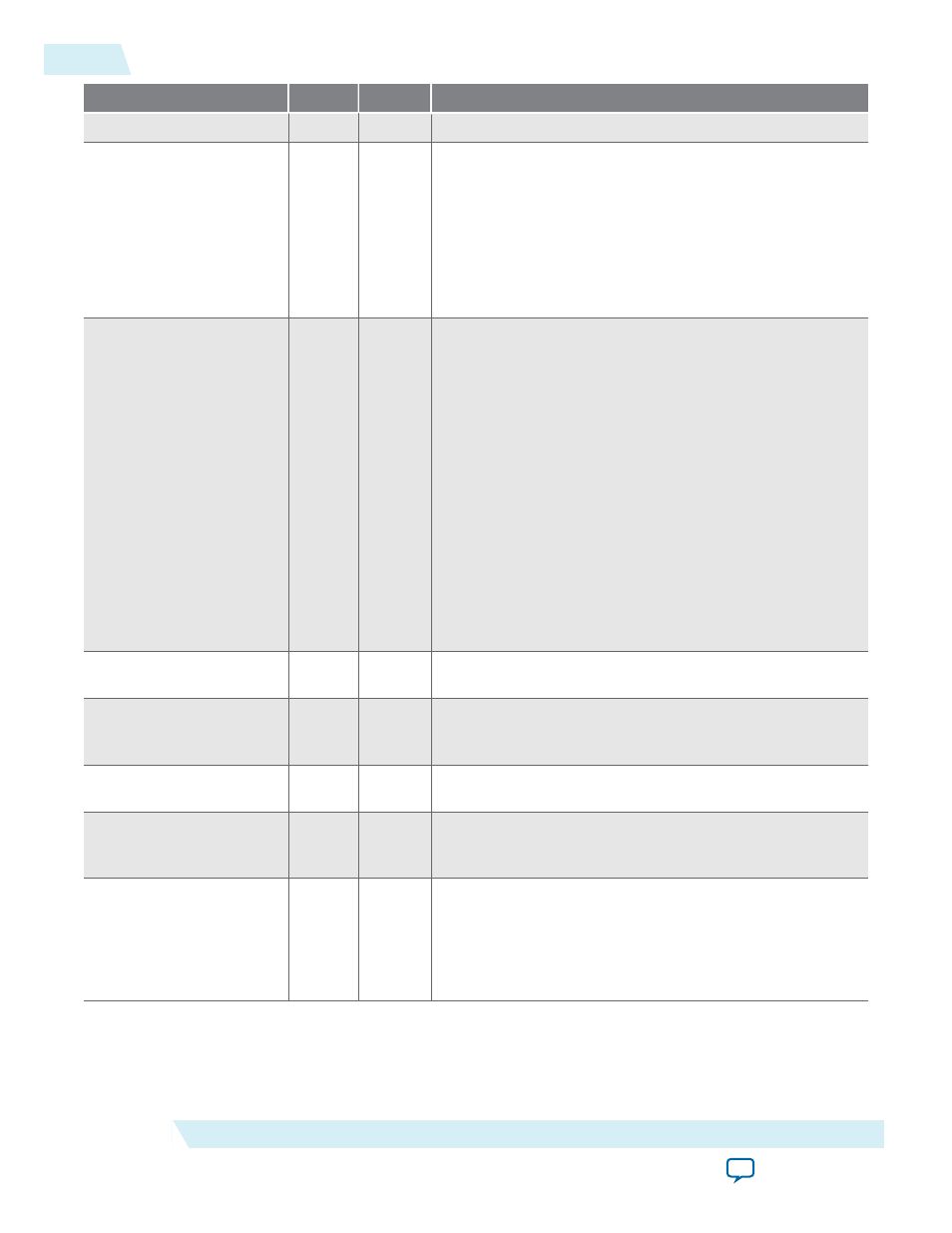

Signal

Type

Required

Description

clocken3

Input Optional Clock enable input for

clock1

port.

aclr0

aclr1

Input Optional Asynchronously clear the registered input and output

ports. The

aclr0

port affects the registered ports that are

clocked by

clock0

clock, while the

aclr1

port affects the

registered ports that are clocked by

clock1

clock.

The asynchronous clear effect on the registered ports can

be controlled through their corresponding asynchronous

clear parameter, such as

outdata_aclr_a

,

address_aclr_

a

, and so on.

eccstatus

Output Optional A 3-bit wide error correction status port. Indicate whether

the data that is read from the memory has an error in

single-bit with correction, fatal error with no correction,

or no error bit occurs.

In Stratix V devices, the M20K ECC status is communi‐

cated with two-bit wide error correction status port. The

M20K ECC detects and fixes a single bit error event or a

double adjacent error event, or detects three adjacent

errors without fixing the errors.

The

eccstatus

port is supported if all the following

conditions are met:

•

operation_mode

parameter is set to

DUAL_PORT

•

ram_block_type

parameter is set to

M144K

or

M20K

•

width_a

and

width_b

parameter have the same value

• Byte enable is not used

data

Input

Yes

Data input to the memory. The data port is required and

the width must be equal to the width of the

q

port.

wraddress

Input

Yes

Write address input to the memory. The

wraddress

port

is required and must be equal to the width of the

raddress

port.

wren

Input

Yes

Write enable input for

wraddress

port. The

wren

port is

required.

rdaddress

Input

Yes

Read address input to the memory. The

rdaddress

port is

required and must be equal to the width of

wraddress

port.

rden

Input Optional Read enable input for

rdaddress

port. The

rden

port is

supported when the

use_eab

parameter is set to

OFF

. The

rden

port is not supported when the

ram_block_type

parameter is set to

MLAB

. Instantiate the ALTSYNCRAM

IP core if you want to use read enable feature with other

memory blocks.

4-4

Signals

UG-01068

2014.12.17

Altera Corporation

Embedded Memory Signals and Parameters