Write and read operations triggering, Write and read operations triggering -2 – Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 12

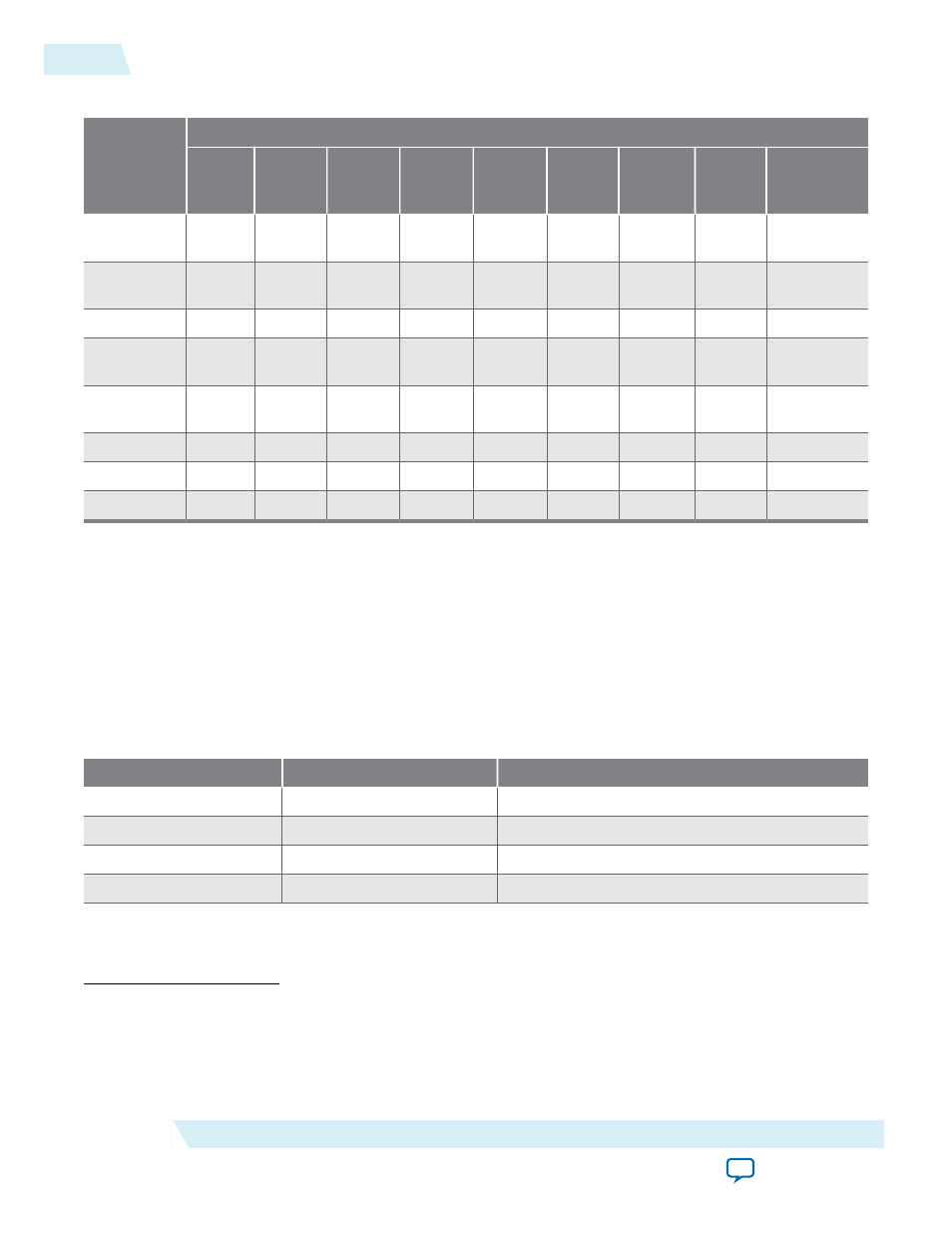

Table 3-1: Embedded Memory Blocks in Altera Devices

Device

Family

Memory Block Type

M512

(512

bits)

(1)

M4K (4

Kbits)

M-RAM

(512

Kbits)

(2)

MLAB

(640 bits)

(3)

M9K (9

Kbits)

M144K

(144

Kbits)

M10K (10

Kbits)

M20K

(20

Kbits)

Logic Cell

(LC)

Arria II

GX

—

—

—

Yes

Yes

—

—

—

Yes

Arria II

GZ

—

—

—

Yes

Yes

Yes

—

—

Yes

Arria V

—

—

—

Yes

—

—

Yes

—

Yes

Cyclone

IV

—

—

—

—

Yes

—

—

—

Yes

Cyclone

V

—

—

—

Yes

—

—

Yes

—

Yes

Max II

—

—

—

—

—

—

—

—

Yes

Stratix IV

—

—

—

Yes

Yes

Yes

—

—

Yes

Stratix V

—

—

—

Yes

—

—

—

Yes

Yes

Note: To identify the type of memory block that the software selects to create your memory, refer to the

Fitter report after compilation.

Write and Read Operations Triggering

The embedded memory blocks vary slightly in its supported features and behaviors. One important

variation is the difference in the write and read operations triggering.

Table 3-2: Write and Read Operations Triggering for Embedded Memory Blocks

This table lists the write and read operations triggering for various embedded memory blocks.

Embedded Memory Blocks

Write Operation

(4)

Read Operation

M10K

Rising clock edges

Rising clock edges

M20K

Rising clock edges

Rising clock edges

M144K

Rising clock edges

Rising clock edges

M9K

Rising clock edges

Rising clock edges

(1)

M512 blocks are not supported in true dual-port RAM mode, and dual-port ROM mode.

(2)

M-RAM blocks are not supported in ROM mode.

(3)

MLAB blocks are not supported in simple dual-port RAM mode with mixed-width port feature, true dual-

port RAM mode, and dual-port ROM mode.

(4)

Write operation triggering is not applicable to ROMs.

3-2

Write and Read Operations Triggering

UG-01068

2014.12.17

Altera Corporation

Embedded Memory Functional Description