Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 28

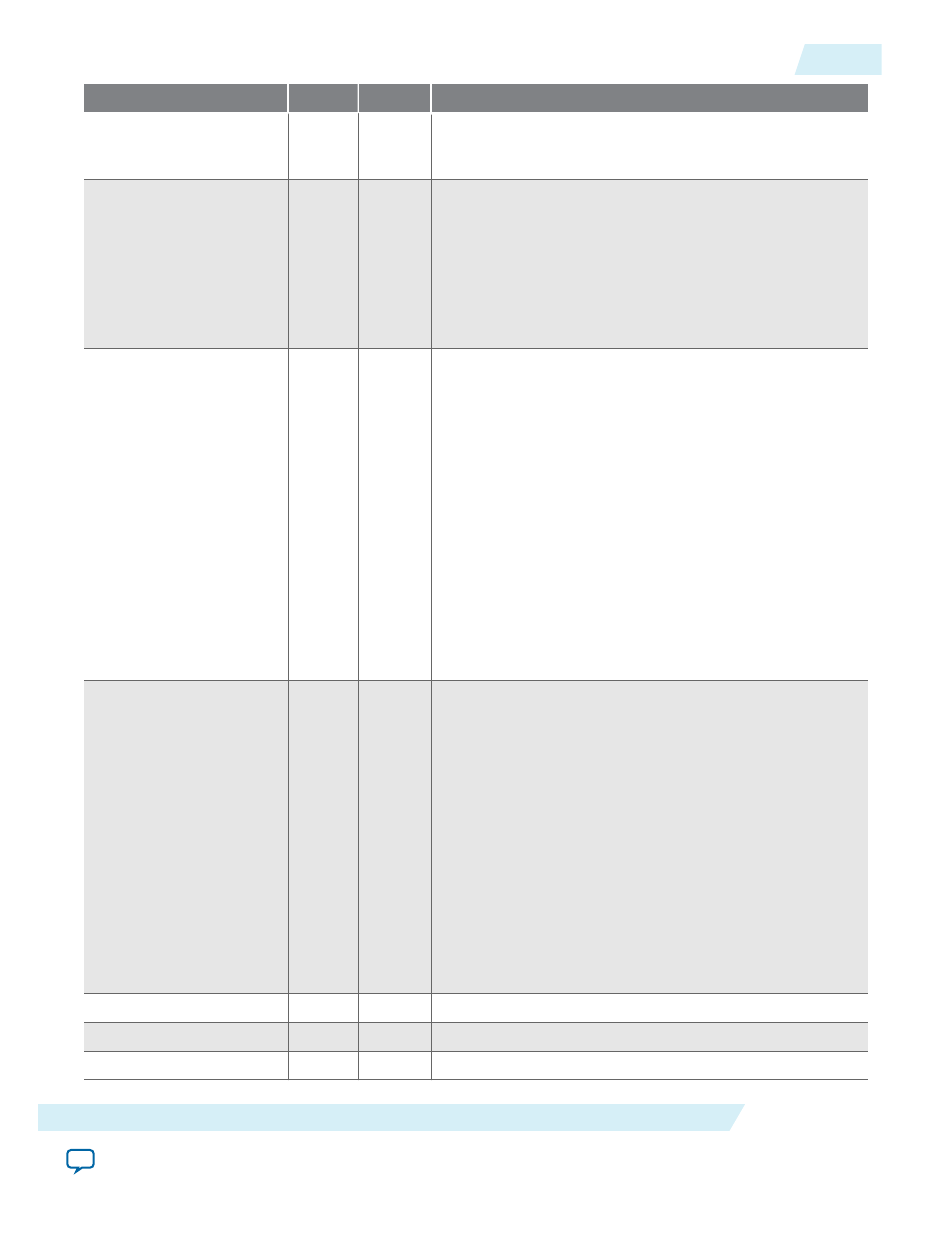

Signal

Type

Required

Description

addressstall_b

Input Optional Address clock enable input to hold the previous address of

address_b

port for as long as the

addressstall_b

port is

high.

q_b

Output

Yes

Data output from port B of the memory. The

q_b

port is

required if the

operation_mode

is set to the following

values:

•

DUAL_PORT

•

BIDIR_DUAL_PORT

The width of

q_b

port must be equal to the width of

data_

b

port.

clock0

Input

Yes

The following describes which of your memory clock must

be connected to the

clock0

port, and port synchronization

in different clocking modes:

• Single clock: Connect your single source clock to

clock0

port. All registered ports are synchronized by

the same source clock.

• Read/Write: Connect your write clock to

clock0

port.

All registered ports related to write operation, such as

data_a

port,

address_a

port,

wren_a

port, and

byteena_a

port are synchronized by the write clock.

• Input Output: Connect your input clock to

clock0

port. All registered input ports are synchronized by the

input clock.

• Independent clock: Connect your port A clock to

clock0

port. All registered input and output ports of

port A are synchronized by the port A clock.

clock1

Input Optional The following describes which of your memory clock must

be connected to the

clock1

port, and port synchronization

in different clocking modes:

• Single clock: Not applicable. All registered ports are

synchronized by

clock0

port.

• Read/Write: Connect your read clock to

clock1

port.

All registered ports related to read operation, such as

address_b

port,

rden_b

port, and

q_b

port are

synchronized by the read clock.

• Input Output: Connect your output clock to

clock1

port. All the registered output ports are synchronized

by the output clock.

• Independent clock: Connect your port B clock to

clock1

port. All registered input and output ports of

port B are synchronized by the port B clock.

clocken0

Input Optional Clock enable input for

clock0

port.

clocken1

Input Optional Clock enable input for

clock1

port.

clocken2

Input Optional Clock enable input for

clock0

port.

UG-01068

2014.12.17

Signals

4-3

Embedded Memory Signals and Parameters

Altera Corporation