Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 42

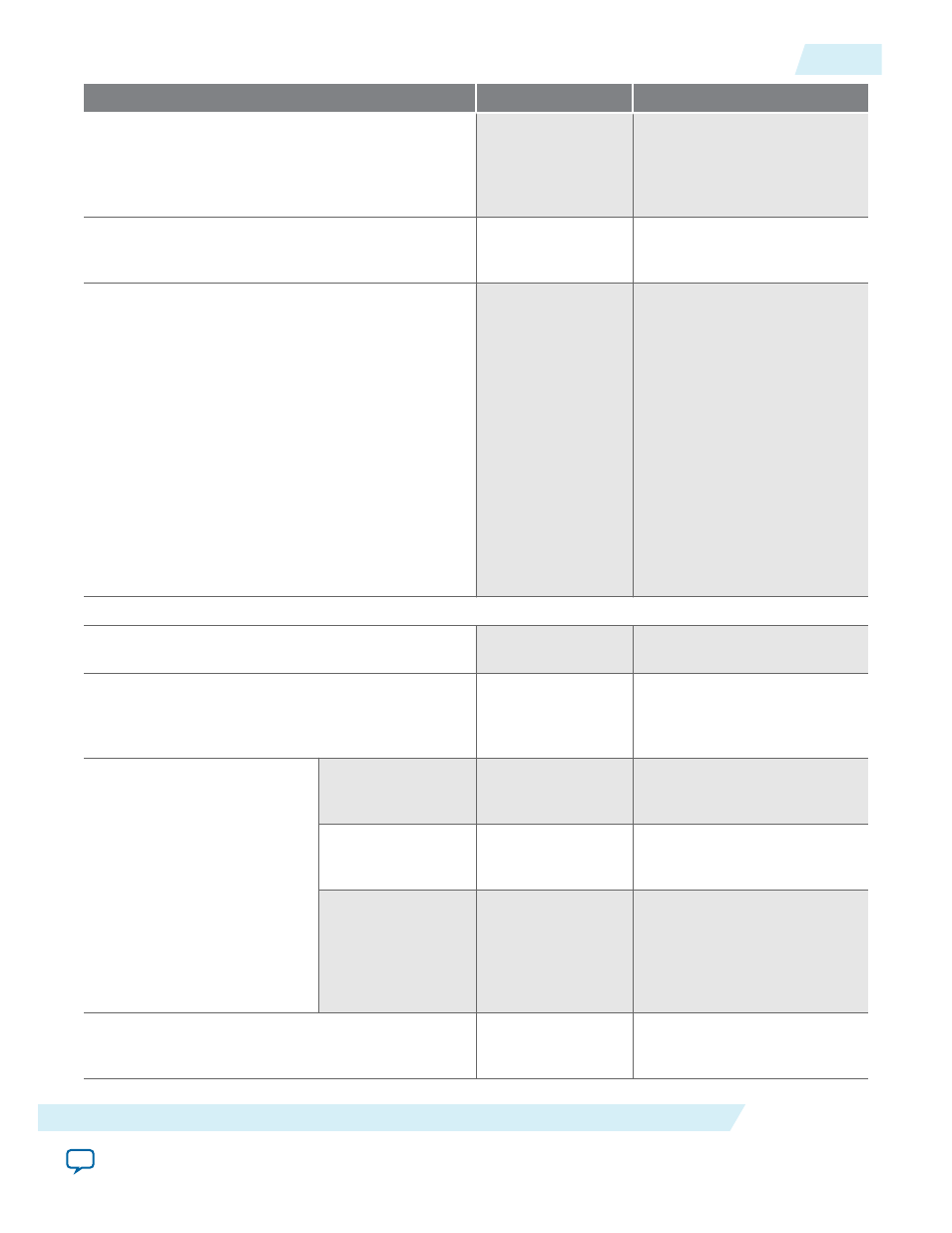

Parameter

Legal Values

Description

What should the memory block type be?

Auto, M4K, M9K,

M144K, M10K,

M20K

Specifies the memory block

type. The types of memory

block that are available for

selection depends on your

target device.

Set the maximum block depth to

Auto, 32, 64, 128,

256, 512, 1024, 2048,

4096

Specifies the maximum block

depth in words.

What clocking method would you like to use?

•

Single clock

•

Dual clock: use

separate ‘input’

and ‘output’

clocks

Specifies the clocking

method to use.

• Single clock—A single

clock and a clock enable

controls all registers of

the memory block

• Dual clock (Input and

Output clock)—The

input clock controls the

address registers and the

output clock controls the

data-out registers. There

are no write-enable, byte-

enable, or data-in

registers in ROM mode.

Parameter Settings: Regs/Clken/Aclrs

Which ports should be registered? ‘q’ output port

On/Off

Specifies whether to register

the ‘q’ output port.

Create one clock enable signal for each clock signal.

Note: All registered ports are controlled by the

enable signal(s)

On/Off

Specifies whether to turn on

the option to create one

clock enable signal for each

clock signal.

More Options

Use clock enable for

port A input

registers

On/Off

Specifies whether to use

clock enable for port A input

registers.

Use clock enable for

port A output

registers

On/Off

Specifies whether to use

clock enable for port A

output registers.

Create an

‘addressstall_a’ input

port.

On/Off

Specifies whether to create a

addressstall_a input port.

You can create this port to

act as an extra active low

clock enable input for the

address registers.

Create an ‘aclr’ asynchronous clear for the

registered ports.

On/Off

Specifies whether to create

an asynchronous clear port

for the registered ports.

UG-01068

2014.12.17

ROM: 1-PORT IP Core Parameters

4-17

Embedded Memory Signals and Parameters

Altera Corporation