Hardware – software development flow, Hardware – software development flow -5 – Altera SoC Embedded Design Suite User Manual

Page 10

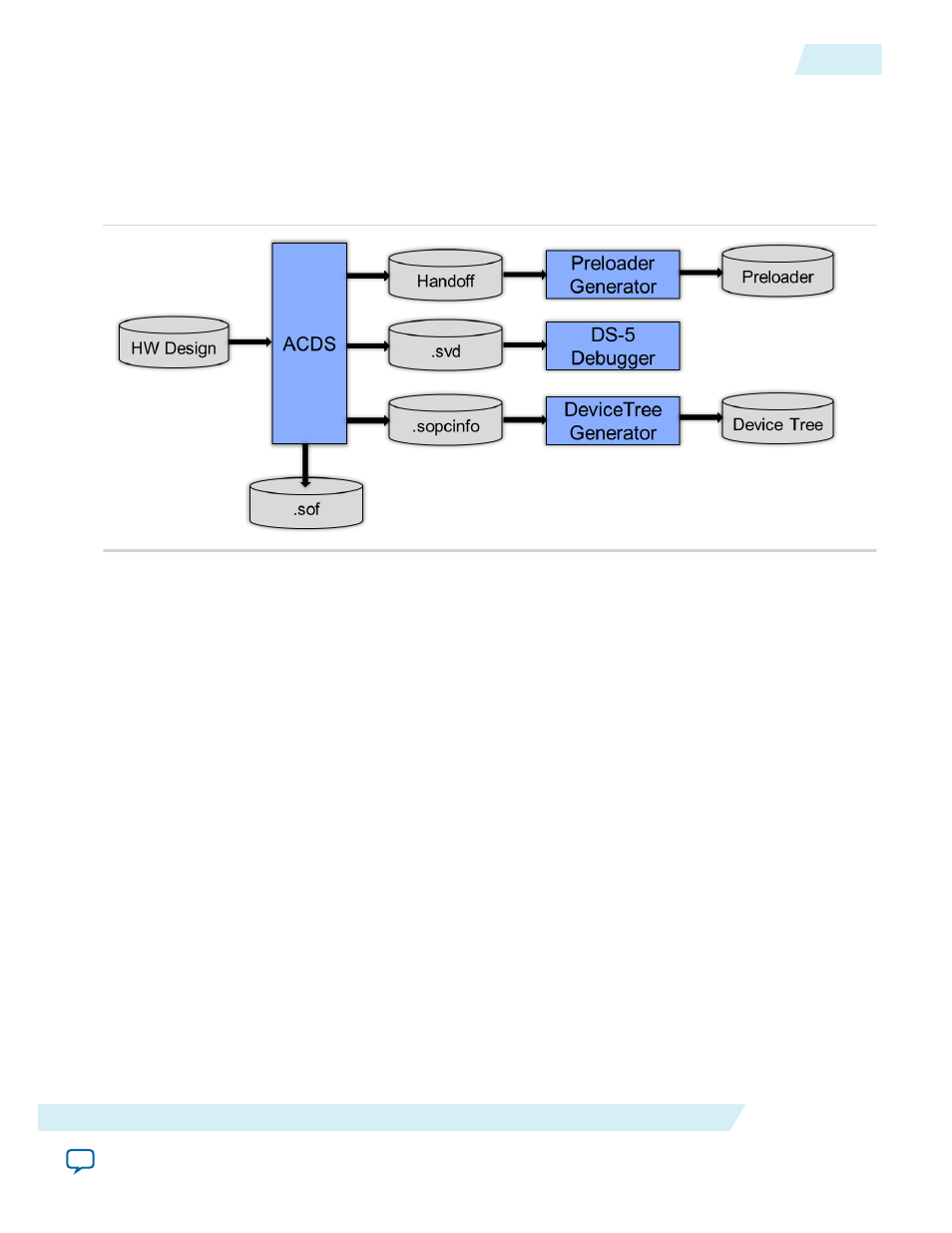

Hardware – Software Development Flow

The Altera hardware-to-software handoff utilities allow hardware and software teams to work independ‐

ently and follow their respective familiar design flows.

Figure 1-1: Altera Hardware-to-Software Handoff

The following handoff files are created when the hardware project is compiled:

• Handoff folder – contains information about how the HPS component is configured, including things

like which peripherals are enabled, the pin MUXing and IOCSR settings, and memory parameters

• .svd file – contains descriptions of the HPS registers and of the soft IP registers on FPGA side

• .sopcinfo file – contains a description of the entire system

The handoff folder is used by the preloader generator to create the Preloader. For more information about

the handoff folder, refer to the HPS Preloader User Guide.

The .svd file contains the description of the registers of the HPS peripheral registers and registers for soft

IP components in the FPGA portion of the SoC. This file is used by the ARM DS-5 Debugger to allow

these registers to be inspected and modified by the user.

SOPC Information (.sopcinfo) file, containing a description of the entire system, is used by the Device

Tree Generator to create the Device Tree used by the Linux kernel. For more information, refer to the

Device Tree Generator chapter.

Note: The soft IP register descriptions are not generated for all soft IP cores.

Related Information

•

•

Device Tree Generator

ug-1137

2014.12.15

Hardware – Software Development Flow

1-5

Introduction to SoC Embedded Design Suite

Altera Corporation