Altera PHYLite User Manual

Page 9

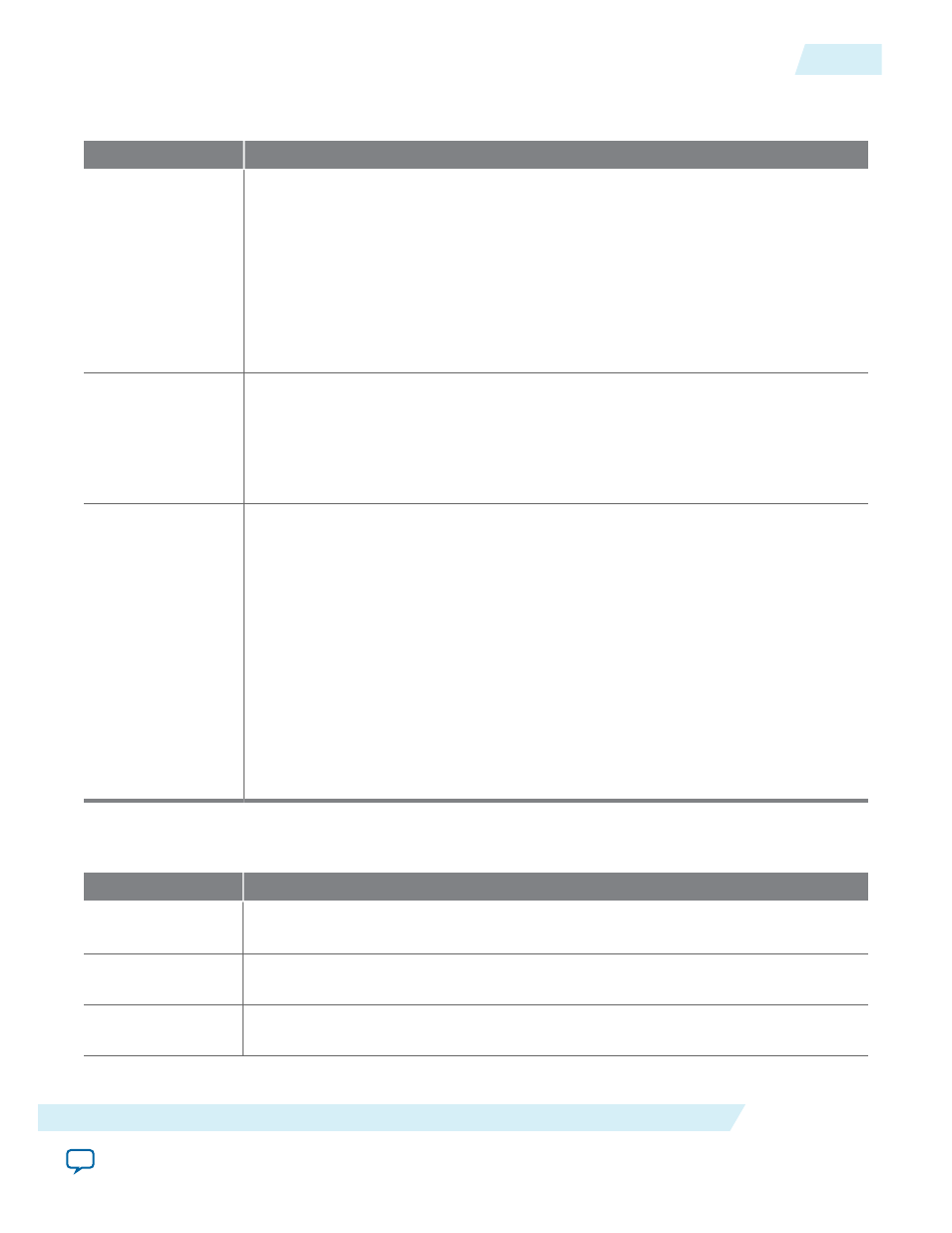

Table 3: Blocks in Data, Strobe, and Read Enable Paths

This table lists the information about these paths.

Path

Description

Data Path

Consists of a PVT compensated delay chain, a DDIO and a read FIFO.

• PVT compensated delay chain—Allows per-bit deskew. You can only control the

PVT compensated delay chain over Avalon-MM interface. For more information,

refer to

• DDIO and read FIFO—Responsible for deserialization with a factor of up to 8 (in

DDR quarter-rate). The transfer between the DDIO and the read FIFO is a zero-

cycle transfer.

The IP core supports SDR input by dropping every other bit of data going to the core.

Strobe Path

Consists of pstamble_reg (a gating component) and a PVT compensated delay chain.

• pstamble_reg—This gating circuitry ensures that only clock edges associated with

valid input data are used.

• PVT compensated delay chain—Provides a phase offset between the strobe and the

data (for example, center aligning edge-aligned inputs).

Read Enable Path Consists of VFIFO, FIFO, and an interpolator.

• VFIFO—takes the

rdata_en

signal from the core and delays it separately for two

outputs, one for the read enable on the read FIFO, and one for the strobe enable.

These delays are calculated at generation time based on the read latency that you

provide. Individual control is not necessary, but if you are modifying these delays

you can do so individually using dynamic reconfiguration.

• FIFO and interpolator—used for the strobe enable delay, the FIFO and interpo‐

lator are identical to the FIFO and interpolator circuitry in the output path. The

FIFO and interpolator are configured to match the output delay for a group with

no additional output delay (Write latency =

0

). During dynamic reconfiguration,

the FIFO and interpolator can be used for fine grained control of the strobe enable

signal. Both of these delays are controlled by the Read latency parameter for the

group.

Table 4: Read Operation Sequence

A read operation is performed as listed in this table.

Operation

1

The core asserts the

read_en

signal (and the external device is issued a read

command)

2

The strobe enable is delayed through the two FIFOs by the programmed read latency

(which should match the latency of the external device)

3

The strobe signal is ungated by the strobe enable signal as valid data enters the read

path

ug_altera_phylite

2015.01.16

Input Path

9

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation