Read latencies, Signals, Clock and reset interface signals – Altera PHYLite User Manual

Page 37

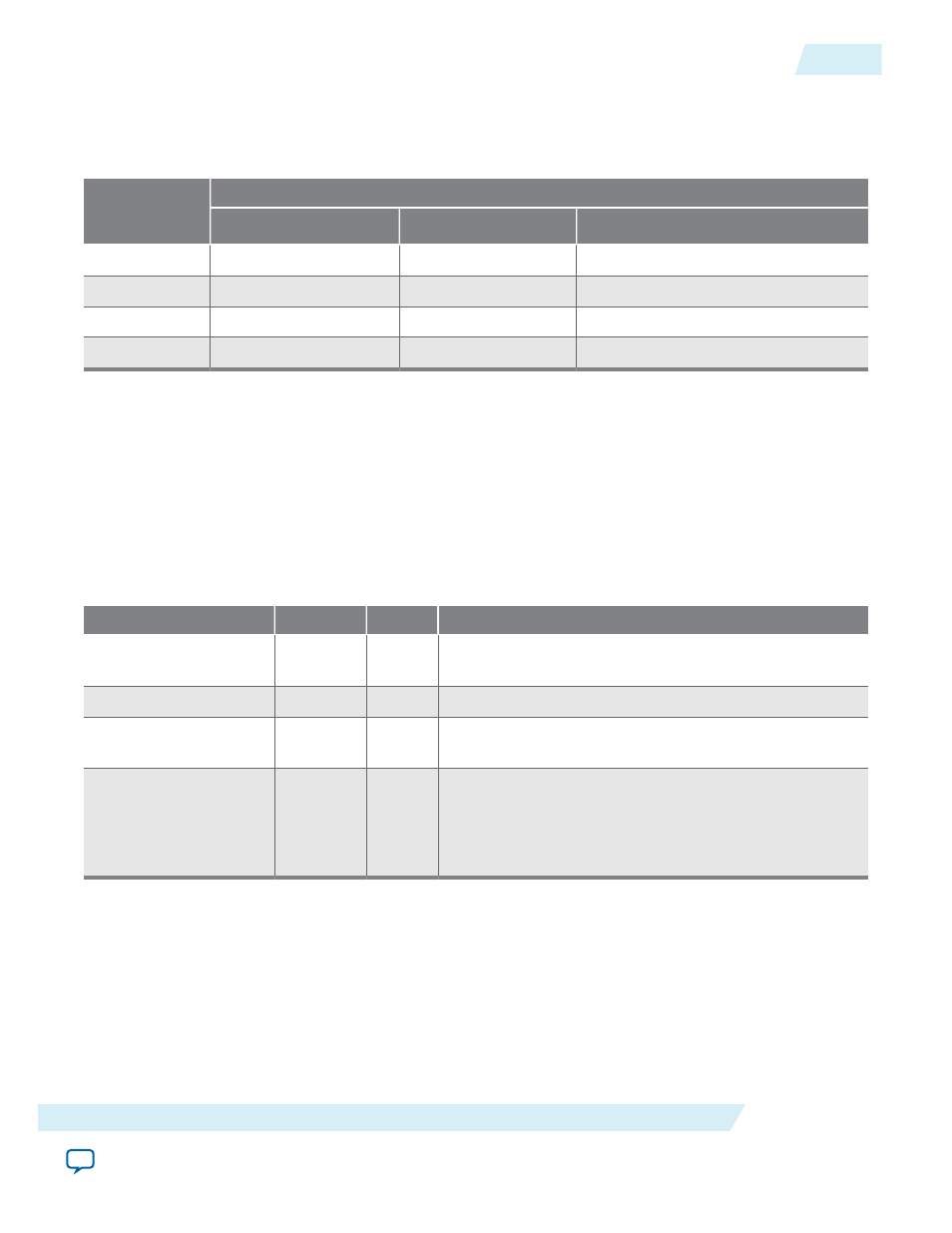

Read Latencies

Table 17: Read Latencies

This table list the read latencies.

VCO Frequency

Multiplication

Factor

Core Clock Rate Setting

Full-Rate

Half-Rate

Quarter-Rate

1

4

5

7

2

4

5

7

4

3

4

7

8

3

4

7

Related Information

VCO Frequency Multiplication Factor

on page 4

Provides information for going from speed grade and external memory frequency to VCO multiplication

factor

Signals

Clock and Reset Interface Signals

Table 18: Clock and Reset Interface Signals

Signal Name

Direction

Width

Description

ref_clk

Input

1

Reference clock for the PLL. The reference clock must be

the same frequency as specified in the parameter.

reset_n

Input

1

Resets the interface. This signal is asynchronous.

interface_locked

Output

1

Interface locked signal from core. This signal indicates

that the PLL and PHY circuitry are locked.

core_clk_out

Output

1

Use this core clock in the core-to-periphery transfer of

soft logic data and control signals.

The

core_clk_out

frequency depends on the interface

frequency and clock rate of user logic parameter.

ug_altera_phylite

2015.01.16

Read Latencies

37

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation