Altera PHYLite User Manual

Page 61

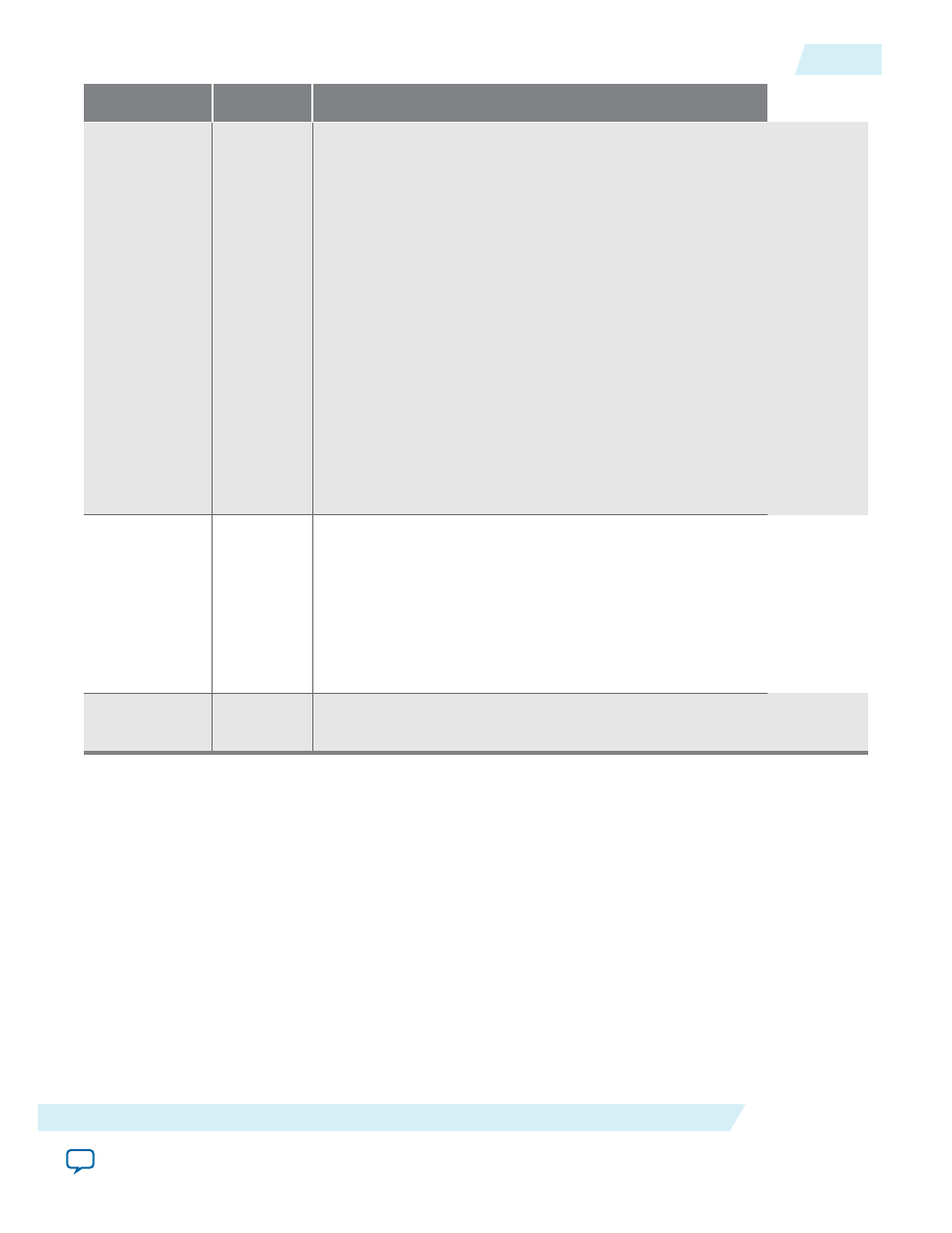

Date

Version

Changes

December,

2014

2014.12.30

• Updated the name of the IP core from Altera PHYLite for

Memory to Altera PHYLite for Parallel Interfaces.

• Updated the maximum clock frequency from 800 MHz to

1333.333 MHz.

• Clarified that to achieve timing closure at 800 MHz and

above, you must use dynamic reconfiguration to calibrate

the interface.

• Added

data_out_n

/

data_io_n

signals to the Output Path

Signals table.

• Added

data_in_n

/

data_io_n

signals to the Input Path

Signals table.

• Updated

data_out

/

data_io

and

data_in

/

data_io

signals in the Input Path Signals and Output Path Signals

tables.

• Updated Parameter Settings table to include Group

Timing Settings information.

• Updated Timing section to include Input Strobe Setup

Delay Constrain and Input Strobe Hold Delay

Constrain parameters information.

August, 2014 2014.08.18

• Renamed the term megafunction to IP core.

• Added information about output path data alignment,

input path data alignment, OCT, I/O standards,

placement restrictions, timing, dynamic reconfiguration.

• Added the PHYLite_delay_calculations.xlsx file.

• Replaced ALTERA_PHYLite_nand_flash_example_

131a10.qar file with nand_flash_example_14.0a10.qar

file.

November,

2013

2013.11.29

Initial release.

ug_altera_phylite

2015.01.16

Document Revision History

61

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation