Example design – Altera PHYLite User Manual

Page 42

Signal Name

Direction

Width

Description

avl_readdata_valid

Output

1

Indicates that read data has returned.

avl_waitrequest

Output

1

Stalls upstream logic when it is asserted.

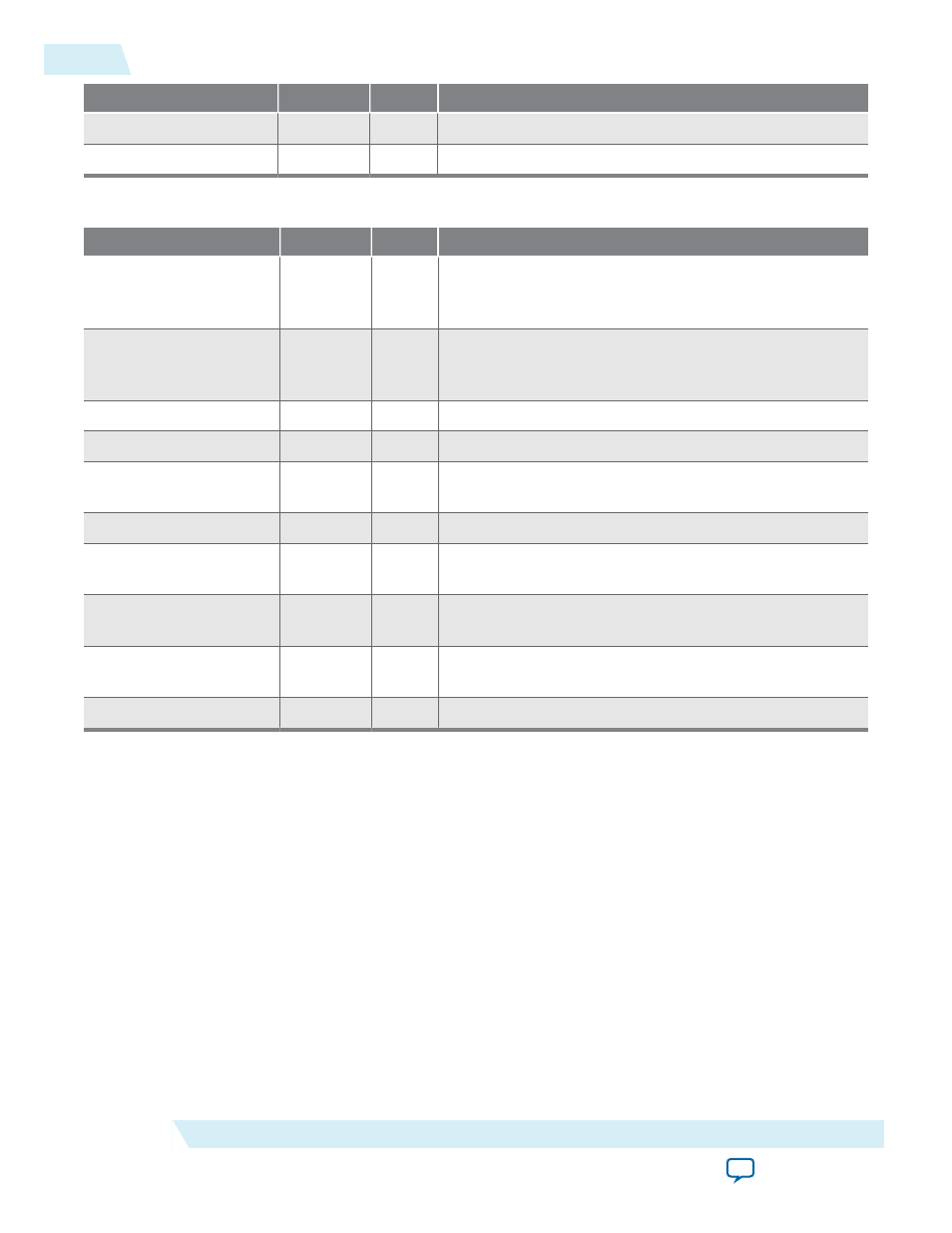

Table 22: Avalon-MM Slave Interface Signals

Signal Name

Direction

Width

Description

avl_out_clk

Output

1

Connect this signal to the input Avalon interface of

another Altera PHYLite for Parallel Interfaces IP core or

the Arria 10 External Memory Interfaces IP.

avl_out_reset_n

Output

1

Connect this signal to the input Avalon interface of

another Altera PHYLite for Parallel Interfaces IP core or

the Arria 10 External Memory Interfaces IP.

avl_out_read

Output

1

Indicates read transaction.

avl_out_write

Output

1

Indicates write transaction.

avl_out_byteenable

Output

4

Controls which bytes should be written on

avl_out_

writedata

.

avl_out_writedata

Output

32

The data packet associated with the write transaction.

avl_out_address

Output

28

Avalon address (in byte granularity). Value is identical to

avl_address

but with zeroes padded on the LSBs.

avl_out_readdata

Input

32

The data packet associated with

avl_out_readdata_

valid

.

avl_out_readdata_

valid

Input

1

Indicates that read data has returned.

avl_out_waitrequest

Input

1

Stalls upstream logic when it is asserted.

Related Information

on page 20

For more information about connecting these signals

Example Design

The Altera PHYLite for Parallel Interfaces IP core is able to generate an example design that matches the

same configuration chosen for the IP. The example design is a simple design that does not target any

specific application; however you can use the example design as a reference on how to instantiate the IP

core and what behavior to expect in a simulation.

Note: The .qsys files are for internal use during example design generation only. You should not edit the

files.

42

Example Design

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide