Calibration guidelines, Strobe enable windowing, Parameter settings – Altera PHYLite User Manual

Page 31

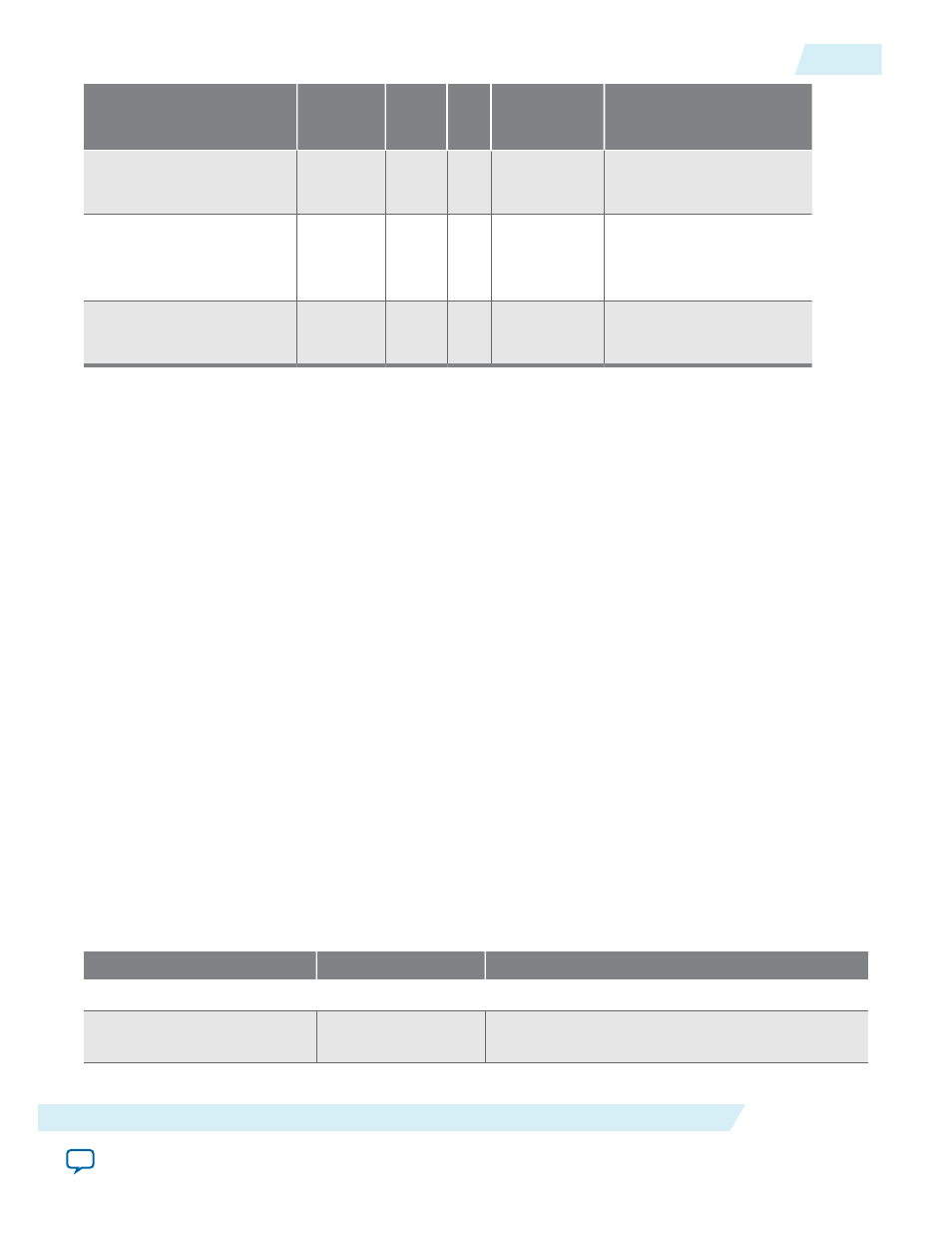

Register[7:0]

Pin[5:0]

Csr[0] Aval

on

R/W

CSR R/W

R/W Data on avl_readdata/

avl_writedata

AVL_CTRL_REG_DQS_

EN_DELAY

0

R: 0/1

W: 0

R/W

R

{26'h0000000,dqs_en_

delay[5:0]}

AVL_CTRL_REG_DQS_

EN_PHASE_SHIFT

0: DQS A

1: DQS B

(6)

R: 0/1

W: 0

R/W

R

{19'h00000,phase[12:0]}

AVL_CTRL_REG_RD_

VALID_DELAY

0

R: 0/1

W: 0

R/W

R

{25'h0000000,rd_vld_

delay[6:0]}

The

interface_id[3:0]

and

grp[4:0]

components of the input address are always used.

Note: VREF reconfiguration is not currently supported by the example design Avalon

controller.

Calibration Guidelines

The Altera PHYLite for Parallel Interfaces IP core allows you to dynamically reconfigure the features of

the interface. However, performing calibration is an application specific process. This section provides

some general guidelines for calibrating the Arria 10 I/O architecture.

Strobe Enable Windowing

The read FIFO has the read pointer reset when reads are far apart (80 core clock cycles). However, the

data inside the FIFO is not cleared. Therefore, an alternating pattern should be used to find the end to the

strobe enable window to avoid erroneous correct reads due to stale data in the FIFO.

The strobe enable turns itself off on the last negative edge of the strobe. Therefore, while finding the

enable window, use extra dummy pulses (either extended strobe or reads from memory without asserting

the

rdata_en

signal) to clear the strobe enable.

Altera PHYLite for Parallel Interfaces IP Core Reference

Parameter Settings

Table 16: Altera PHYLite for Parallel Interfaces IP Core Parameter Settings

This table lists the parameter settings for the Altera PHYLite for Parallel Interfaces IP core.

GUI Name

Values

Description

Parameter

Number of groups

1 to 18

Number of data/strobe groups in the interface.

The value is set to 1 by default.

ug_altera_phylite

2015.01.16

Calibration Guidelines

31

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation