Altera PHYLite User Manual

Page 52

To begin, follow these steps:

1. In the Quartus II software version 14.0a10, open the

.

2. In the Quartus II dialog box, click Yes.

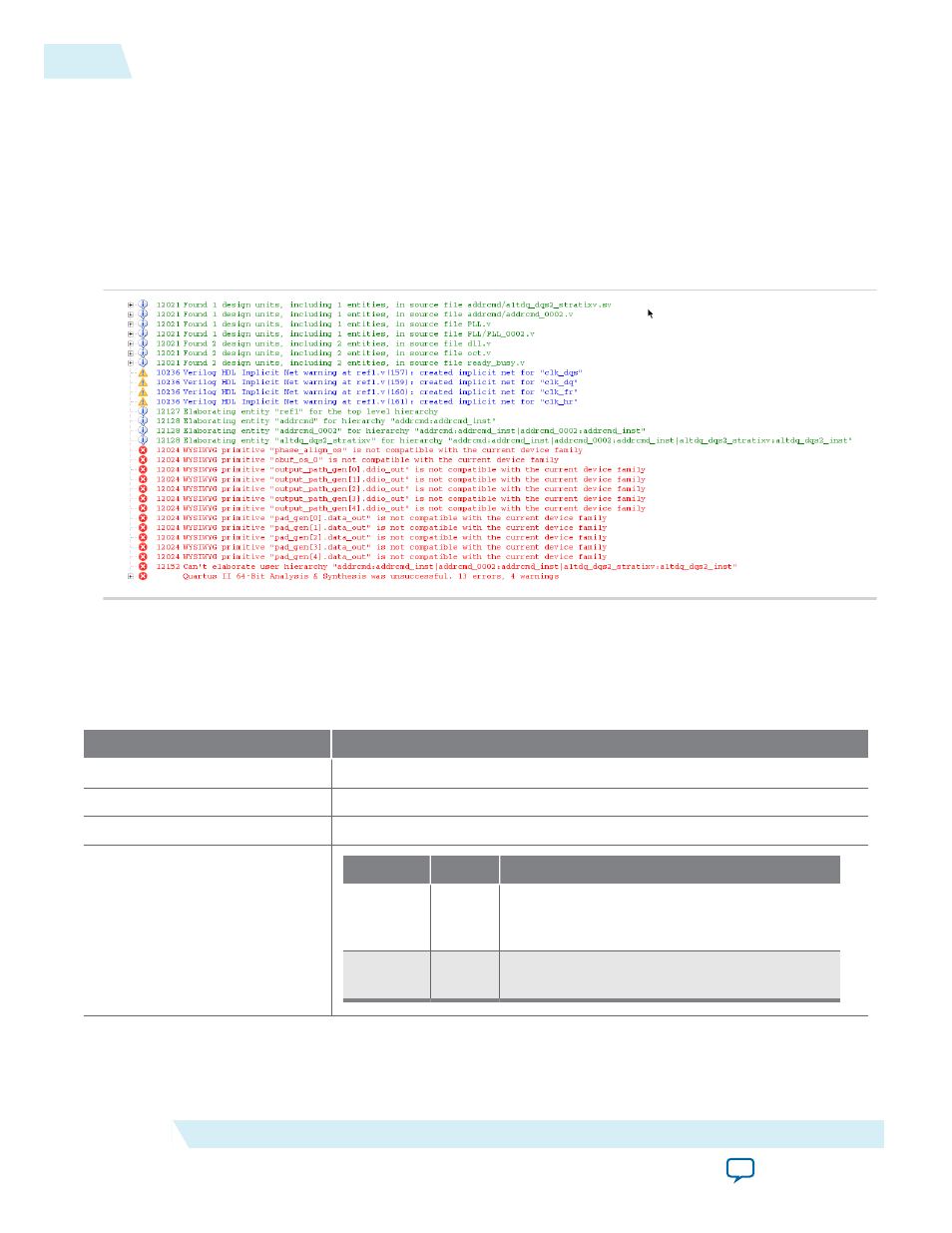

3. Run Analysis and Synthesis. The following figure shows the generated error messages, indicating that

there is no direct migration support from the ALTDQ_DQS2 IP core to the Altera PHYLite for Parallel

Interfaces IP core. To manually migrate to the Altera PHYLite for Parallel Interfaces IP core,

understanding the ALTDQ_DQS2 design is crucial.

Figure 26: Error Message

Basic NAND Flash Protocol

Table 26: Details of the Micron MT29F NAND Flash Memory Datasheet

This table lists the details of the Micron MT29F NAND Flash memory datasheet (focusing on synchronous

mode):

Synchronous Signals

Description

Memory frequency

100MHz

Data pin width

8-bit

Data Mode

DDR

DQx and DQS

Signal

Type

Description

DQx

I/O

Data inputs/outputs. The bidirectional I/Os

transfer address, data, and command

information.

DQS

I/O

Data strobe. Provides a synchronous

reference for data input and output.

52

Example Design: Manual IP Migration from ALTDQ_DQS2 IP Core to the Altera

PHYLite for Parallel Interfaces IP Core

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide