Kontron AT8050 User Manual

Page 144

A-8

www.kontron.com

A.4.1.3

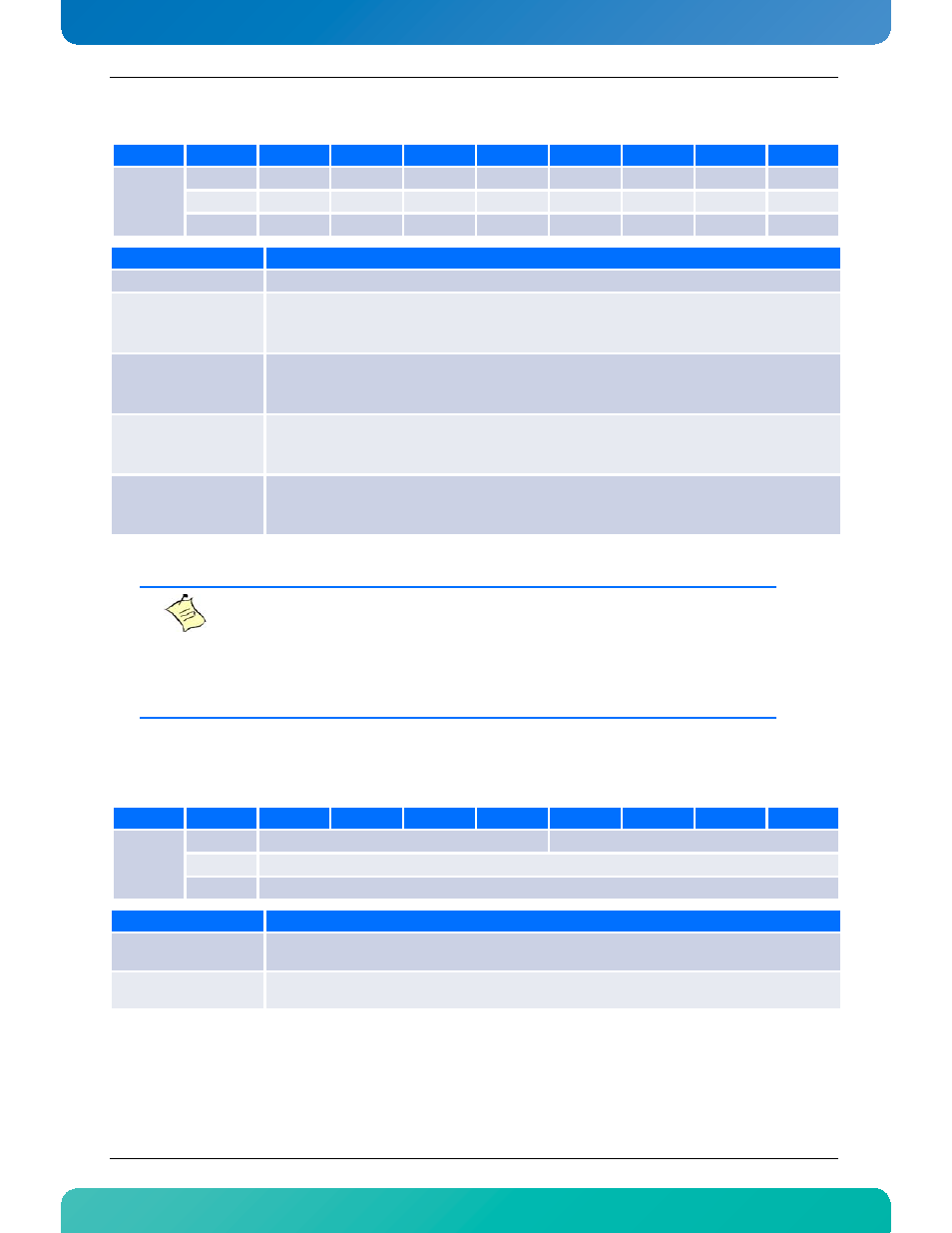

Base + 02h TelClock2: AMCs Clock Enables & Frequency Selection

A.4.1.4

Base + 03h TelClock3: PLD Configuration & Version

Offset

Action

D7

D6

D6

D4

D3

D2

D1

D0

02h

Read

B2TCF

B2TAF

B2TCEN

B2TAEN

B1TCF

B1TAF

B1TCEN

B1TAEN

Write

B2TCF

B2TAF

B2TCEN

B2TAEN

B1TCF

B1TAF

B1TCEN

B1TAEN

Reset

0

0

0*

0*

0

0

0*

0*

Name

Description

B2*

Reserved for AMC-B2 (for board that have two AMCs).

B1TCF

AMC-B1 TCLK Frequency

1: use 8kHz frame pulse from PLL

0: use 19.44MHz from PLL

B1TAF

AMC-B1 TCLKA Frequency

1: use 8kHz frame pulse from PLL

0: use 19.44MHz from PLL

B1TCEN

AMC-B1 TCLKC Enable. This bit is forced to 0 when the AMC is in fault or removed.

1: drive AMC-B1 clock TCLKC

0: don’t drive AMC-B1 TCLKC

B1TAEN

AMC-B1 TCLKA Enable. this bit is forced to 0 when the AMC is in fault or removed.

1: drive AMC-B1 clock TCLKA

0: don’t drive AMC-B1 TCLKA

Note:

If the clock source of the PLL is 19.44MHz, the phase of this clock is unrelated to any other 8kHz

clock in the system.

The AMC has to be present and fully powered for the enable bits to be settable. On a unexpected

extraction (user doesn't wait for the blue LED), the hardware automatically clears bits B1TCEN and

B1TAEN in case a user would extract and re-insert immediatly the AMC.

Offset

Action

D7

D6

D6

D4

D3

D2

D1

D0

03h

Read

PLD_CONFIG

PLD_VERSION

Write

NA

Reset

NA

Name

Description

CONFIG

Circuit configuration that the PLD expect. For the interface and circuit described in this document,

this field is away 0000. If the PLD is abscent or not programmed, this field will return 0000.

VERSION

Code version of the PLD for the above configuration. If the PLD is absent or not programmed, this field

will return 0000.