A.4.1 register description – Kontron AT8050 User Manual

Page 142

A-6

www.kontron.com

A.4.1

Register Description

A.4.1.1

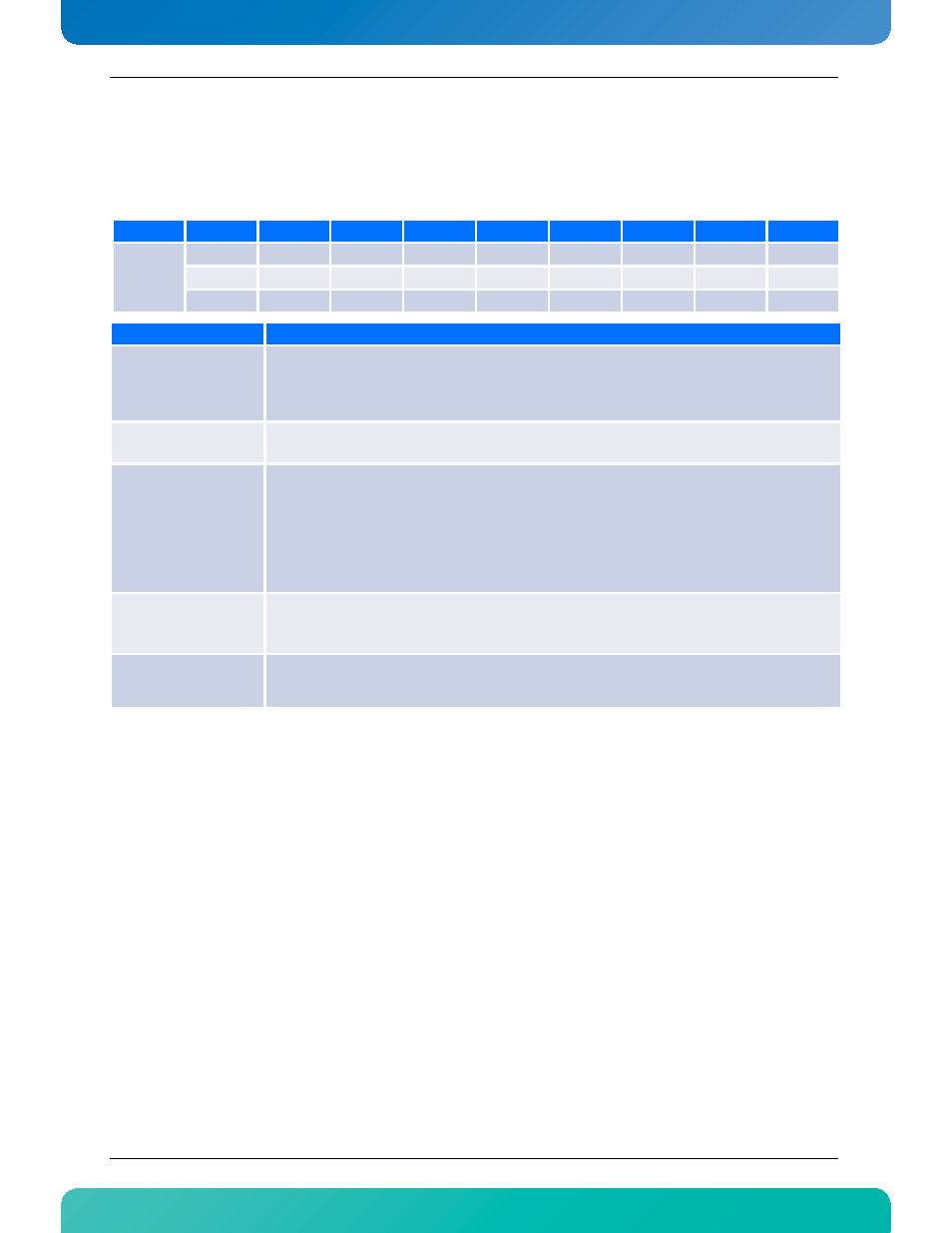

Base + 00h TelClock0: Backplane Clock Status, PLL Reference &

Interface Selection

Offset

Action

D7

D6

D6

D4

D3

D2

D1

D0

00h

Read

IFSEL

MAN

SEL_REFA

BP_REF

CLK2B

CLK2A

CLK1B

CLK1A

Write

IFSEL*

MAN

SEL_REFM

BP_REF

NU

NU

NU

NU

Reset

0

0

0

0

NA

NA

NA

NA

Name

Description

IFSEL

Interface selection. This bit is always writable from the IPMC side but on the LPC side, the CPU can only

read it.

1: IPMC has write control of the interface

0: Main CPU (LPC) has write control of the interface

MAN

0: The PLD chooses automatically the reference used by the DPLL (CLKA or B).

1: Selection of the DPLL reference is manual. Write the selection in bit SEL_REF.

SEL_REFA

SEL_REFM

On a read, return the reference automatically selected by the CPLD:

0: REF0 is the reference used by the PLL (i.e. CLKA)

1: REF1 is the reference used by the PLL (i.e. CLKB)

When bit MAN=1, the application software can select the reference by writing the desired value in this

bit. This bit is not writtable when MAN=0. Note that on a read, this bit returns the automatic selection

event if MAN=1.

BP_REF

Backplane selection of clock to connect to the PLL.

0: Use backplane CLK1A and CLK1B (8kHz)

1: Use backplane CLK2A and CLK2B (19.44MHz)

CLK1A/B

CLK2A/B

Coarse monitoring status. A1 indicate that the corresponding backplane clock is present. A0, that it is

absent. Those statuses are valid only if CLK1A/B is 8kHz and CLK2A/B is 19.44MHz. If other

frequencies are used, those bits should be ignored.