Typed write (write block), Unprotected bit write – Rockwell Automation 1770, D17706.5.16 Ref Mnl DF1 Protocol Command User Manual

Page 117

7–30

Communication Commands

Publication 1770Ć6.5.16 - October 1996

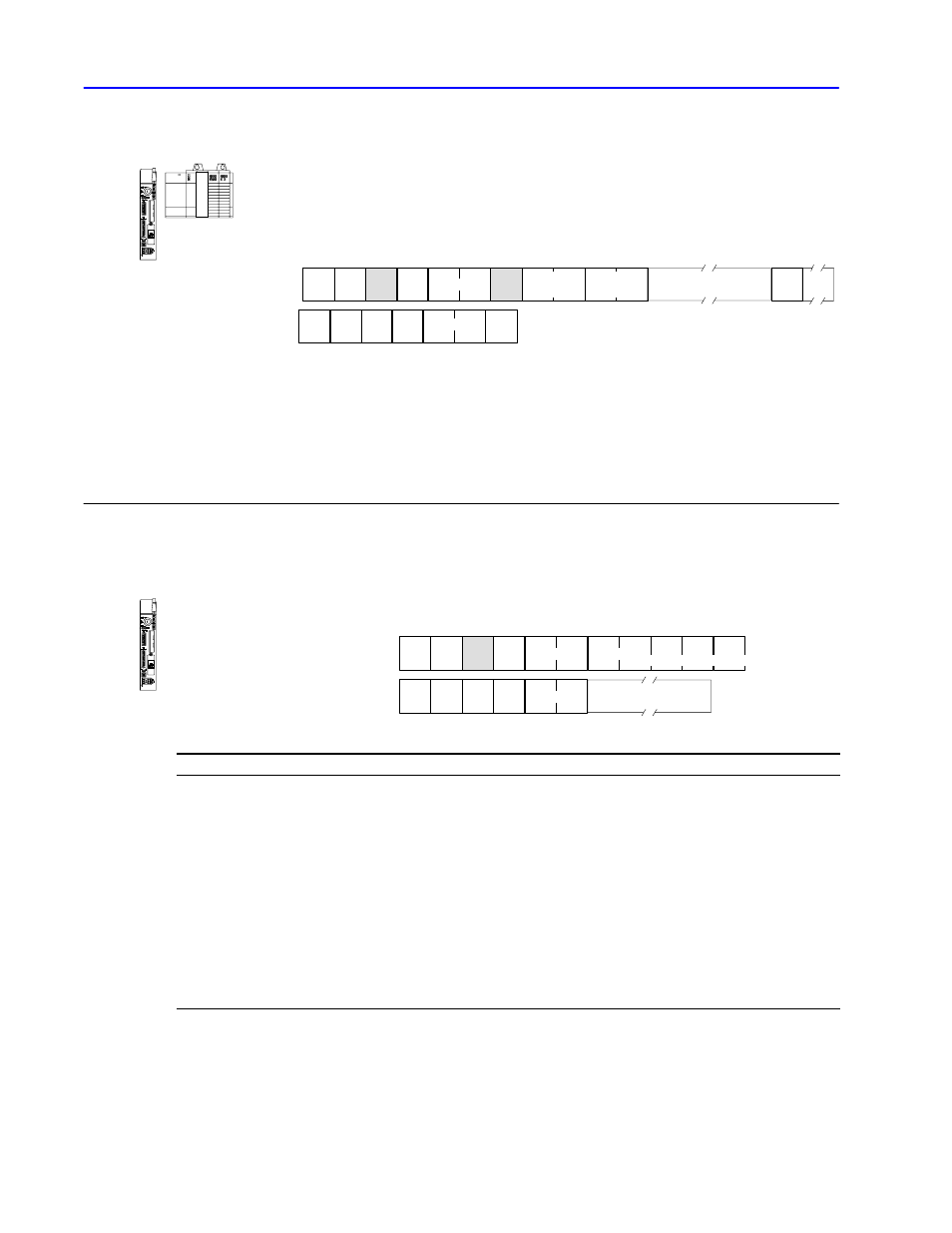

typed write (write block)

Writes a block of data to the processor starting at the PLC-5 system

address plus the packet offset. The type of data sent with the typed

write command must match the data type of the file to which it is

being written. If not, the remote host returns an error reply.

CMD

0F

STS

FNC

67

TNS

C

CMD

4F

STS

EXT

STS

R

DST SRC

SRC DST

A

Packet

Offset

PLCĆ5 sys. address

Total

Trans

B

A - Type/data parameter

B - Data (up to 240 bytes minus the number of bytes used in the PLCĆ5 system address and the type/data parameter.)

An EXT STS byte will replace A and B if there is an error.

The EXT STS field may be attached to the reply packet only when there is an error.

For packet offset, total transaction, and size (in elements) low byte is first.

The PLCĆ5 system address can be a logical binary address or a logical ASCII address that contains up to 51 bytes of

specification.

TNS

unprotected bit write

Sets or resets individual bits in any area of PLC data table memory.

C

CMD

05 STS

TNS

ADDR

R

STS

TNS

CMD

45

Data (max. 244 bytes)

Set

Reset

Up to 60 masks of this form.

DST SRC

SRC DST

DATA

ADDR

SET

RESET

DATA is:

•

4Ćbyte blocks, each of

which contains a 16Ćbit

address field

•

Use ADDR to specify the

address of the byte to be

modified in the PLC data

table memory.

•

Use SET to specify which

bits to set to 1 in the

addressed PLC byte.

•

Use RESET to specify

which bits to reset to 0 in

the addressed PLC byte.

address field

•

a set mask

•

a reset mask

•

Put the low byte (least

significant bits) of the PLC

address value into the first

byte of the ADDR field.

•

A 1 in a bit position of the

SET mask means to set

the corresponding bit in the

addressed PLC byte to 1.

•

A 1 in a bit position of the

RESET mask means to

reset the corresponding bit

in the addressed PLC byte

to 0.

•

A 0 in a bit position of the

SET mask means to leave

the corresponding bit in the

PLC byte unchanged.

•

A 0 in a bit position of the

RESET mask means to

leave the corresponding bit

in the PLC byte

unchanged.

•

PLCĆ5

•

PLCĆ5/VME

•

SLC 5/03

•

SLC 5/04

•

1774ĆPLC

•

PLCĆ2

•

PLCĆ3

•

PLCĆ5