B.80 status:questionable[:event]? query, B.81 status:questionable:condition? query, B.82 status:questionable:enable command – KEPCO ATE-DMG SERIES User Manual

Page 89: B.83 status:questionable:enable? query, B.84 system:error[:next]? query, B.80, B.81, B.82, B.83, B.84

ATE-DMG 042314

B-19

B.80

STATus:QUEStionable[:EVENt]? QUERY

STAT:QUES?

Syntax:

Short Form: STAT:QUES[EVEN]?

Long Form: STATus:QUEStionable[EVENT]?

Return Value:

Description: Indicates questionable events that occurred since previous STAT:QUES? query. Returns the

value of the Questionable Event register (see Table B-3). The Questionable Event register is a

read-only register which holds (latches) all events. Reading the Questionable Event register clears it.

(See example, Figure B-7.)

B.81

STATus:QUEStionable:CONDition? QUERY

STAT:QUES:COND?

Syntax:

Short Form: STAT:QUES:COND?

Long Form: STATus:QUEStionable:CONDition?

Return Value:

Description: Returns the value of the Questionable Condition Register (see Table B-3). The Questionable

Condition Register contains unlatched real-time information about questionable conditions of the

power supply. Bit set to 1 = condition (active, true); bit reset to 0 = condition (inactive, false). (See

example, Figure B-7.)

B.82

STATus:QUEStionable:ENABle COMMAND

STAT:QUES:ENAB

Syntax:

Short Form: STAT:QUES:ENAB

Function:

Programs Questionable Condition Enable Register.

Description: Programs Questionable Condition Enable Register (see Table B-3).The Questionable Condition

Enable Register determines which conditions are allowed to set the Questionable Condition Register;

it is a mask for enabling

specific bits in the Questionable Event register that can cause the question-

able summary bit (bit 3) of the Status Byte register to be set. The questionable summary bit is the log-

ical OR of all the enabled bits in the Questionable Event register

.

Bit set to 1 = function enabled

(active, true); bit reset to 0 = function disabled (inactive, false)

.

(See example, Figure B-7.)

B.83

STATus:QUEStionable:ENABle? QUERY

STAT:QUES:ENAB?

Syntax:

Short Form: STAT:QUES:ENAB? Long Form: STATus:QUESionable:ENABle?

Return Value:

Description: Reads Questionable Condition Enable Register (see Table B-3). Power supply returns value of

Questionable Condition Enable Register, indicating which conditions are being monitored. Bit set to 1

= function enabled (active, true); bit reset to 0 = function disabled (inactive, false)

.

Related Com-

mands: STAT:QUES?. (See example, Figure B-7.)

B.84

SYSTem:ERRor[:NEXT]? QUERY

SYST:ERR?

Syntax:

Short Form: SYST:ERR[:NEXT]?

Long Form: SYSTem:ERRor[:NEXT]?

Return Value:

Description: Posts error messages to the output queue. Returns the next error number followed by its corre-

sponding error message string from the instrument error queue. The error queue is a FIFO (first in first

out) buffer that stores errors as they occur. As it is read, each error is removed from the queue and the

next error message is made available. When all errors have been read, the query returns 0,”No error”.

If more than 15 errors are accumulated, it will overflow. The oldest errors stay in the queue but the

most recent errors are discarded. The last error in the queue will be -350,”Too many errors.” Error

messages are defined in Table B-4.

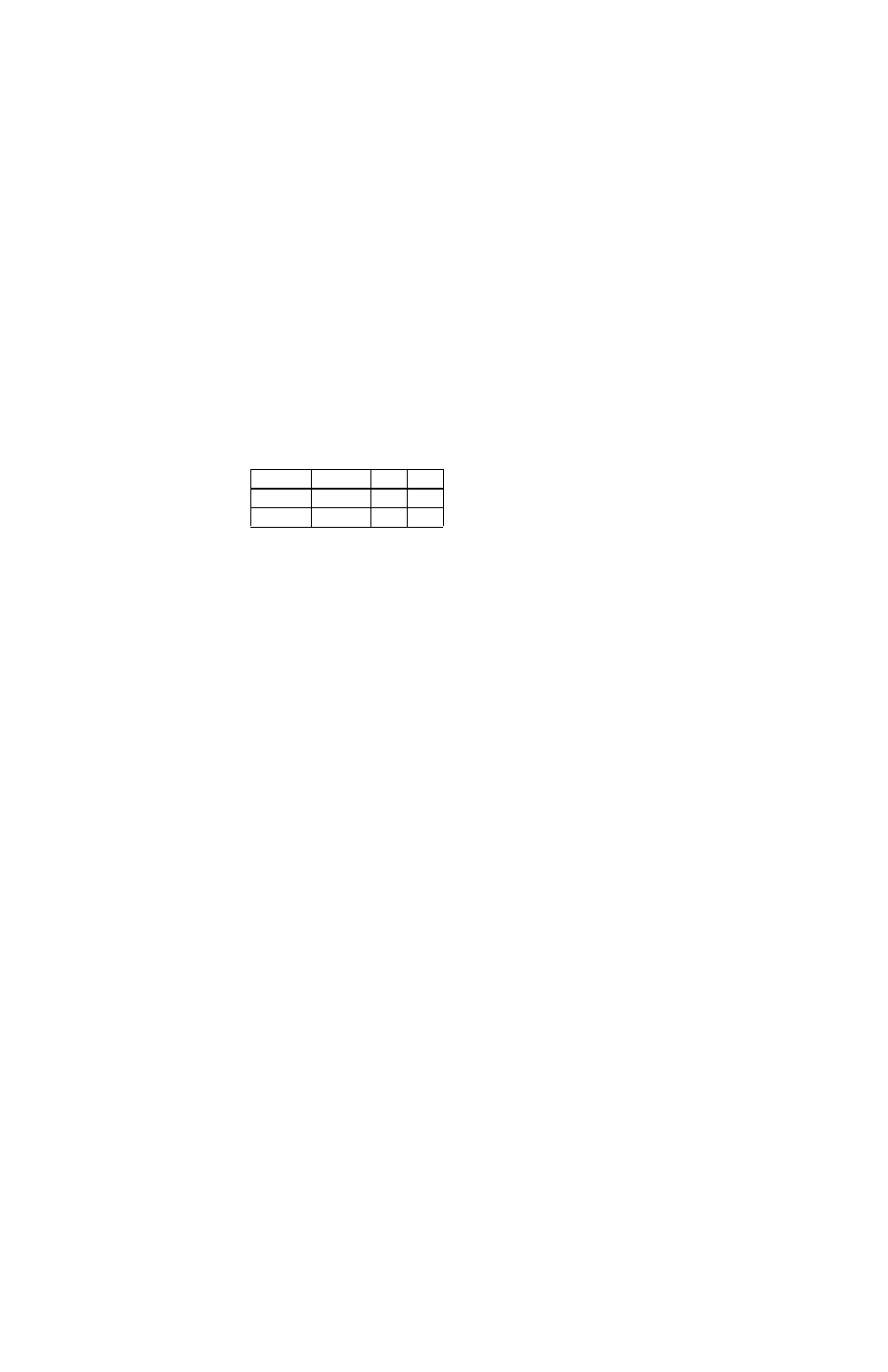

TABLE B-3. QUESTIONABLE EVENT REGISTER, QUESTIONABLE CONDITION REGISTER

AND QUESTIONABLE CONDITION ENABLE REGISTER BITS

CONDITION

NU

OC

OV

BIT

15 - 2

1

0

VALUE

32,768 - 4

2

1

OC - OVERCURRENT PROTECTION TRIPPED

OV - OVERVOLTAGE PROTECTION TRIPPED

NU - NOT USED