Teledyne LeCroy Voyager Exerciser Generation Script Language Manual User Manual

Page 154

Teledyne LeCroy

Voyager USB 3.0 Exerciser Generation Script Language Reference Manual

145

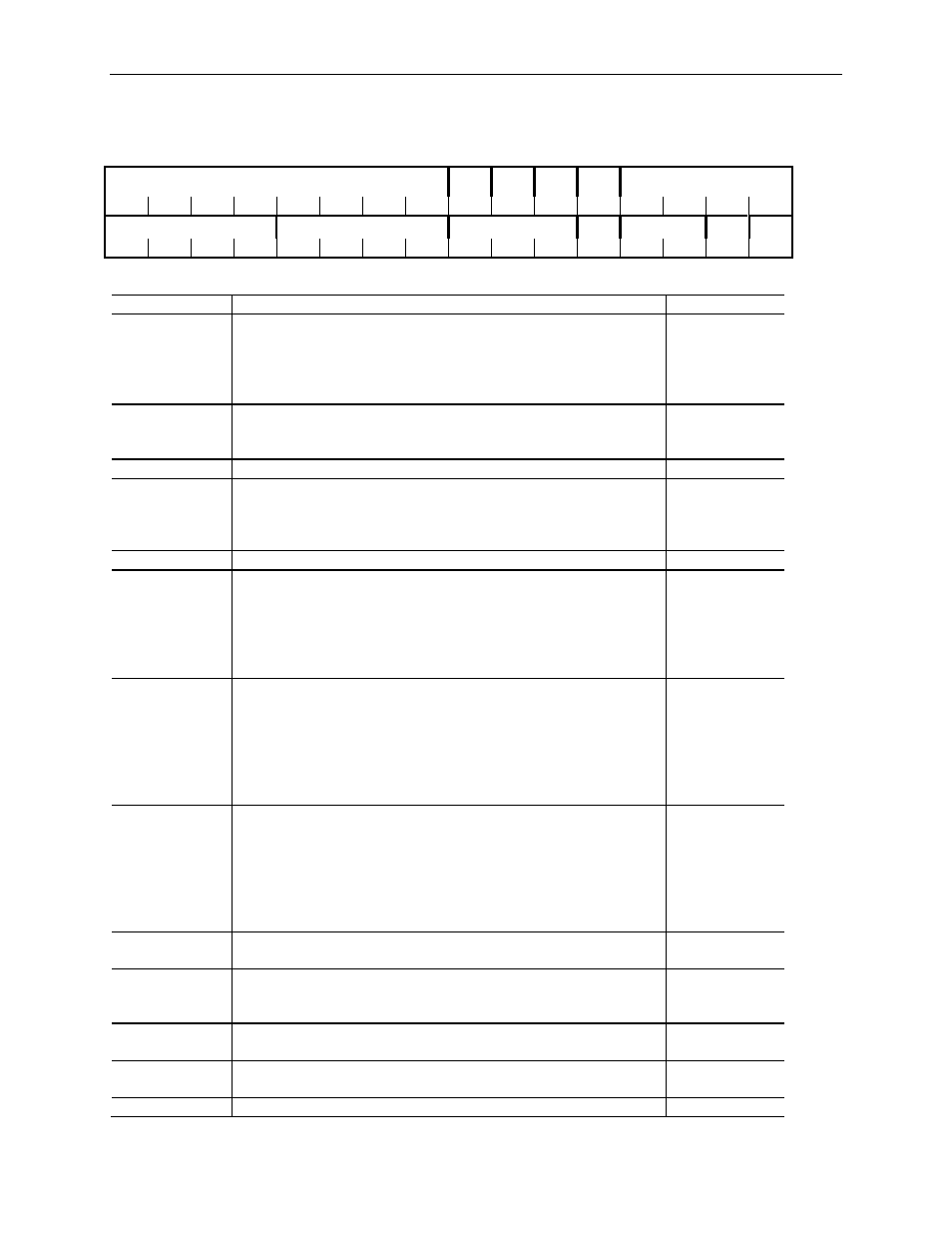

This command contains all applicable error injections for the LMP packets.

MSB

LSB

Reserved

WAT

SEC

CF

G

CAP

HSN

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

CRC-16

CRC-5

Reserved

DON

E

Reserved

INF

EN

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit Location

Register Description

Attributes

0

EN

0: Disable (stop error injection), 1: Enable (run error

injection)

This bit will be cleared automatically when the INF bit is not

set and requested error injection is done.

RW

1

INF

0: Run the command once, on the first series of LMP

generation, 1: Run the command until the EN bit is set.

RW

3:2

Reserved, filled by 0

RO

4

DONE

This bit shows that the error has been injected at least once

from the last time EN has been set. It will be cleared

whenever a value 1 is written to EN.

RO

7:5

Reserved, filled by 0

RO

11:8

CRC-5

Bit 0 (bit 8 of whole DW); 1: Disable auto CRC-5 calculation

Bit 1 (bit 9 of whole DW); 0: Run for limited number of times

specified in register Error! Reference source not found.,

: Run for infinite number of times until the Bit 0 is set.

Bits 3:2 (bits 11:10 of whole DW); reserved for future.

RW

15:12

CRC-16

Bit 0 (bit 12 of whole DW); 1: Disable auto CRC-16

calculation

Bit 1 (bit 13 of whole DW); 0: Run for limited number of time

specified in Error! Reference source not found. register,

: Run for infinite number of time until the Bit 0 is set.

Bits 3:2 (bits 15:14 of whole DW); reserved for future.

RW

19:16

HSN (Header Sequence Number)

Bit 0 (bit 16 of whole DW); 1: Disable auto LCW Header

Sequence Number manipulation

Bit 1 (bit 17 of whole DW); 0: Run for limited number of time

specified in Error! Reference source not found. register,

: Run for infinite number of time until the Bit 0 is set.

Bits 3:2 (bits 19:18 of whole DW); reserved for future.

RW

20

CAP

Don’t send Port Capability LMP upon entering U0

RW

21

CFG

Don’t send Port Configuration LMP (or Port Configuration

Response LMP) upon entering U0

RW

22

SEC

insert error setting only on second LMP

RW

23

WAT

Wait for Port capability for both host and device mode

RW

31:24

Reserved, filled by 0

RO