4 power manager state description, 1 powerdown state – Rainbow Electronics AT73C246 User Manual

Page 29

29

11050A–PMAAC–07-Apr-10

AT73C246

11.4 Power Manager State Description

AT73C246 ICs are available with 2 factory programmed power sequences. The following timing

diagrams refer to “SEQUENCE A” and “SEQUENCE B” programmed ICs as defined in section

17. “Ordering Information” on page 154

. See also the structure of register “VERSION (0x7F)”.

11.4.1

POWERDOWN STATE

When AT73C246 is in POWERDOWN state:

• Only V

BACKUP

supply is active. VDD

{0,1,2,3,4}

power supplies are OFF.

• Audio function is OFF.

• ADC function is OFF.

• RSTB pin is held low.

• Led pin is set as input with internal 120k pull-up resistor to VINSYS.

• TWI registers are reset to default value.

When the POWERDOWN state is reached from the RUN state, the CPU power supplies are

switched off sequentially as described in

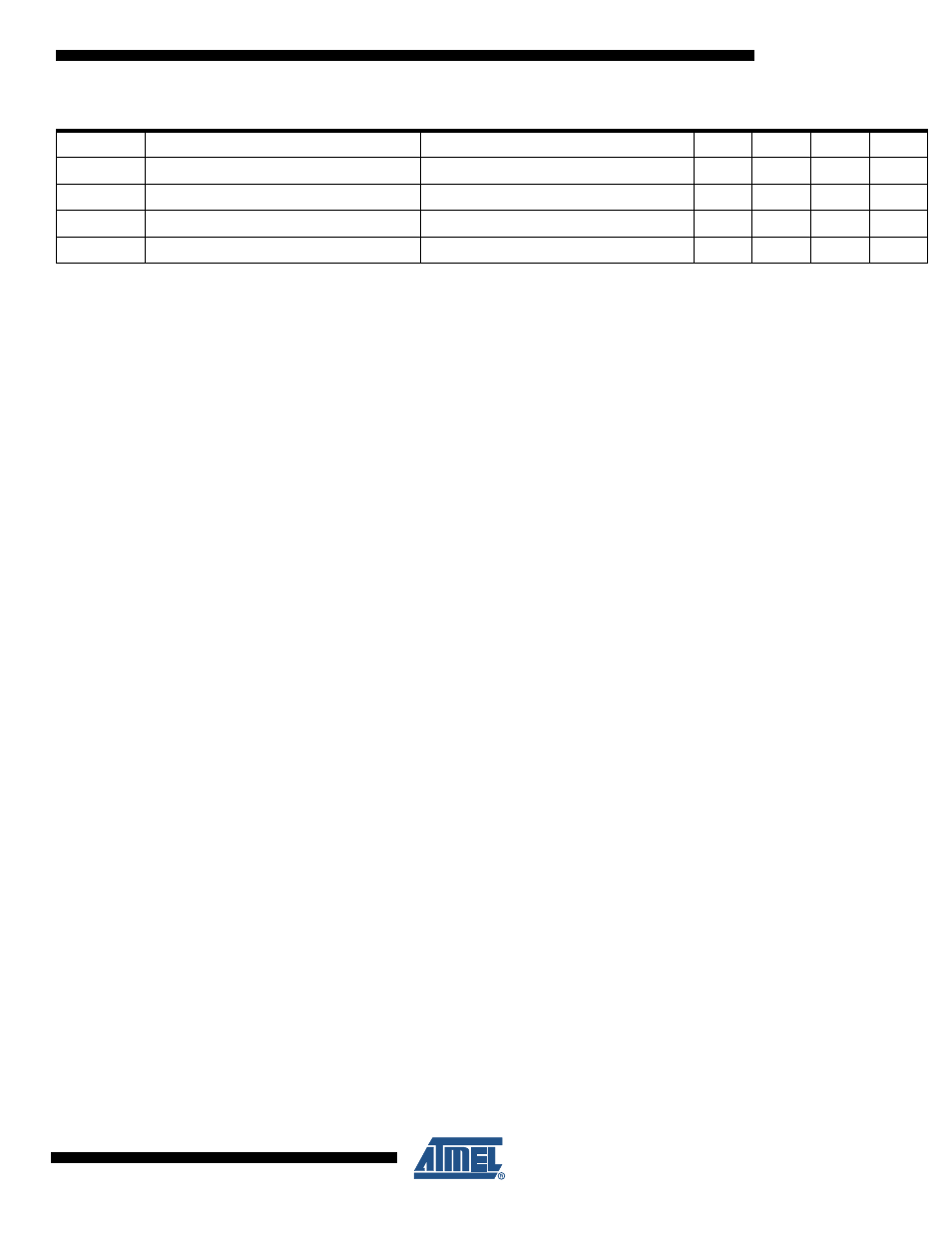

WAKEUP0

Pin pulsed to V

BACKUP

Level. Pulse Width.

Pin used as WAKEUP event

5

-

-

ns

WAKEUP1

Pin pulsed to V

PAD

Level. Pulse Width.

Pin used as WAKEUP event

5

-

-

ns

WAKEUP2

Pin pulsed to V

PAD

Level. Pulse Width.

Pin used as WAKEUP event

5

-

-

ns

WAKEUP3

Pin pulsed to V

PAD

Level. Pulse Width.

Pin used as WAKEUP event

5

-

-

ns

Table 11-1.

EVENTS Timing Table

Pin

Parameter

Comments

Min

Typ

Max

Units