Universal serial interface – usi, Overview, Attiny26(l) – Rainbow Electronics ATtiny26L User Manual

Page 63: Three-wire synchronous data transfer (master, f, 2, slave f, Data received interrupt, Wakeup from idle mode

63

ATtiny26(L)

1477B–AVR–04/02

Universal Serial

Interface – USI

The Universal Serial Interface, or USI, provides the basic hardware resources needed

for serial communication. Combined with a minimum of control software, the USI allows

significantly higher transfer rates and uses less code space than solutions based on

software only. Interrupts are included to minimize the processor load. The main features

of the USI are:

•

Two-wire Synchronous Data Transfer (Master or Slave, f

SCLmax

= f

CK

/16)

•

Three-wire Synchronous Data Transfer (Master, f

SCKmax

= f

CK

/2, Slave f

SCKmax

= f

CK

/4)

•

Data Received Interrupt

•

Wakeup from Idle Mode

•

In Two-wire Mode: Wake-up from All Sleep Modes, Including Power-down Mode

•

Two-wire Start Condition Detector with Interrupt Capability

Overview

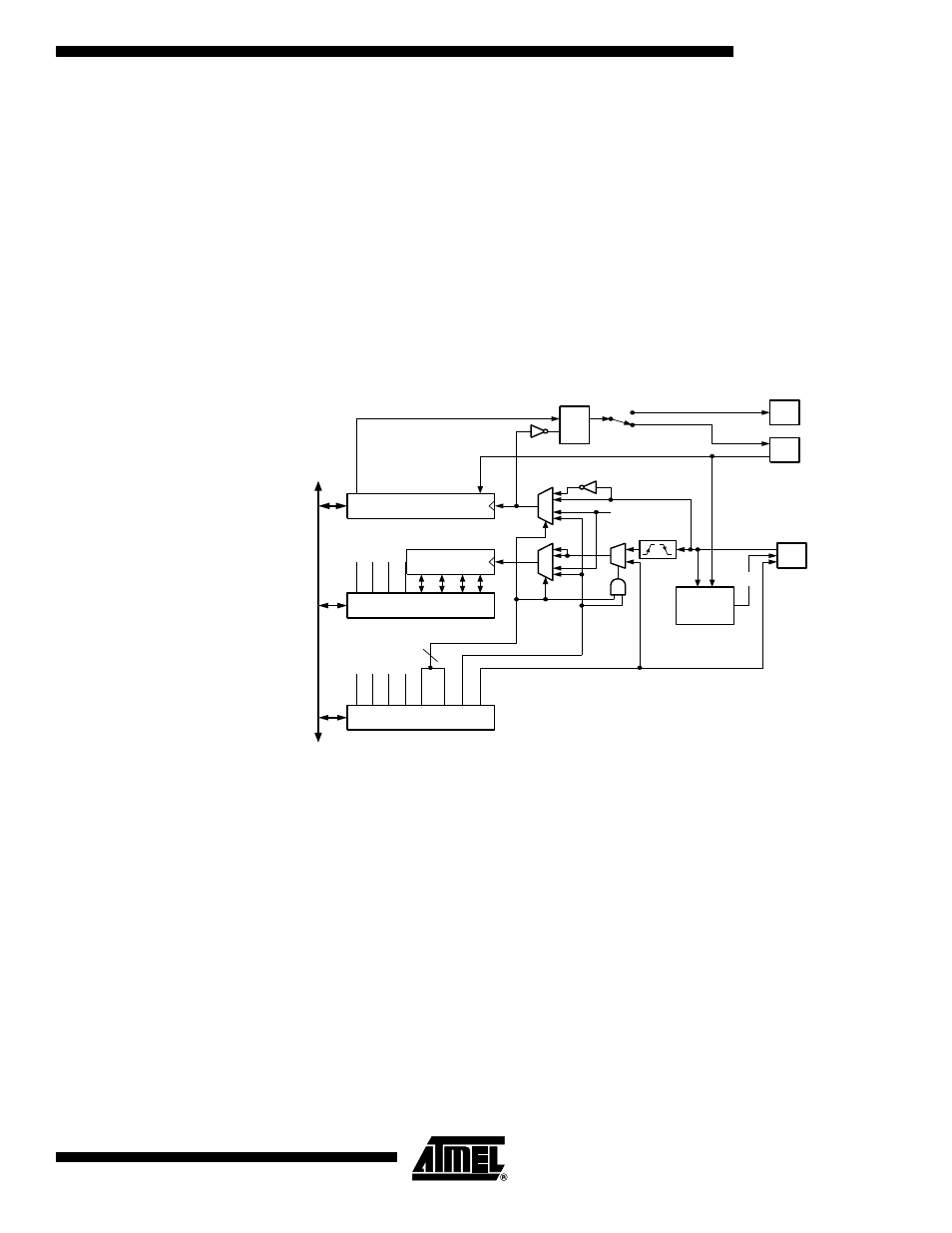

A simplified block diagram of the USI is shown on Figure 39.

Figure 39. Universal Serial Interface, Block Diagram

The 8-bit Shift Register is directly accessible via the data bus and contains the incoming

and outgoing data. The register has no buffering so the data must be read as quickly as

possible to ensure that no data is lost. The most significant bit is connected to one of two

output pins depending of the wire mode configuration. A transparent latch is inserted

between the serial register output and output pin, which delays the change of data out-

put to the opposite clock edge of the data input sampling. The serial input is always

sampled from the Data Input (DI) pin independent of the configuration.

The 4-bit counter can be both read and written via the data bus, and can generate an

overflow interrupt. Both the serial register and the counter are clocked simultaneously

by the same clock source. This allows the counter to count the number of bits received

or transmitted and generate an interrupt when the transfer is complete. Note that when

an external clock source is selected the counter counts both clock edges. In this case

the counter counts the number of edges, and not the number of bits. The clock can be

selected from three different sources: the SCK pin, Timer 0 overflow, or from software.

The Two-wire clock control unit can generate an interrupt when a start condition is

detected on the Two-wire bus. It can also generate wait states by holding the clock pin

low after a start condition is detected, or after the counter overflows.

DATA BUS

USIPF

USITC

USICLK

USICS0

USICS1

USIOIF

USIOIE

USIDC

USISIF

USIWM0

USIWM1

USISIE

B

it7

Two-wire Clock

Control Unit

PB0

PB1

PB2

DO

(Output only)

DI/SDA

(Input/Open Drain)

SCK/SCL

(Input/Open Drain)

4-bit Counter

USIDR

USISR

D Q

LE

USICR

CLOCK

HOLD

TIM0 OVF

Bit0

[1]

3

0

1

2

3

0

1

2

0

1

2