Attiny26(l) – Rainbow Electronics ATtiny26L User Manual

Page 40

40

ATtiny26(L)

1477B–AVR–04/02

• Bits 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the

corresponding interrupt mask is set (one). The activity on the external INT0 pin that acti-

vates the interrupt is defined in the following table.

Note:

1. When changing the ISC10/ISC00 bits, INT0 must be disabled by clearing its Interrupt

Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are

changed.

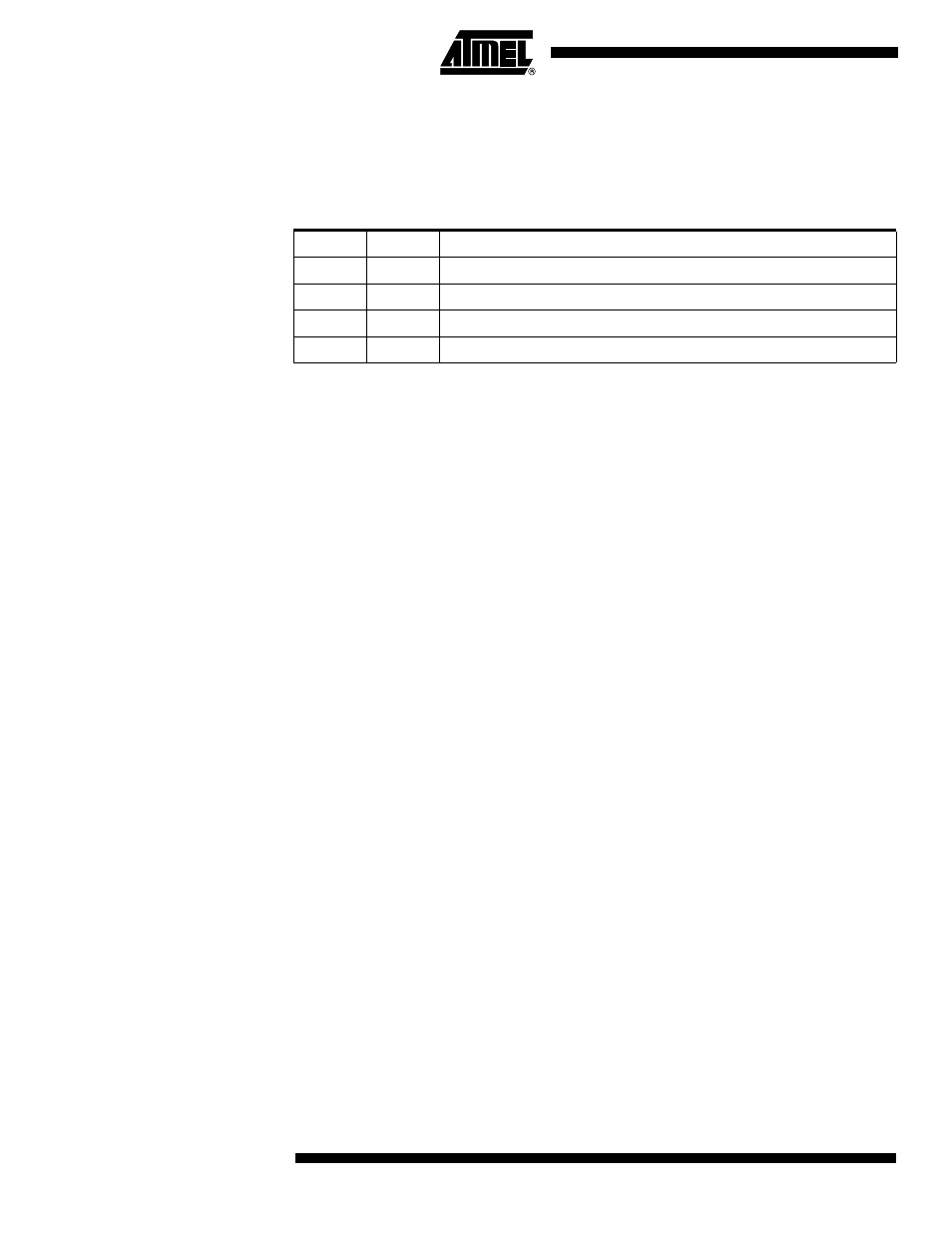

Table 19. Interrupt 0 Sense Control

ISC01

ISC00

Description

0

0

The low level of INT0 generates an interrupt request.

0

1

Any change on INT0 generates an interrupt request.

1

0

The falling edge of INT0 generates an interrupt request.

1

1

The rising edge of INT0 generates an interrupt request.

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)