Attiny26(l) – Rainbow Electronics ATtiny26L User Manual

Page 48

48

ATtiny26(L)

1477B–AVR–04/02

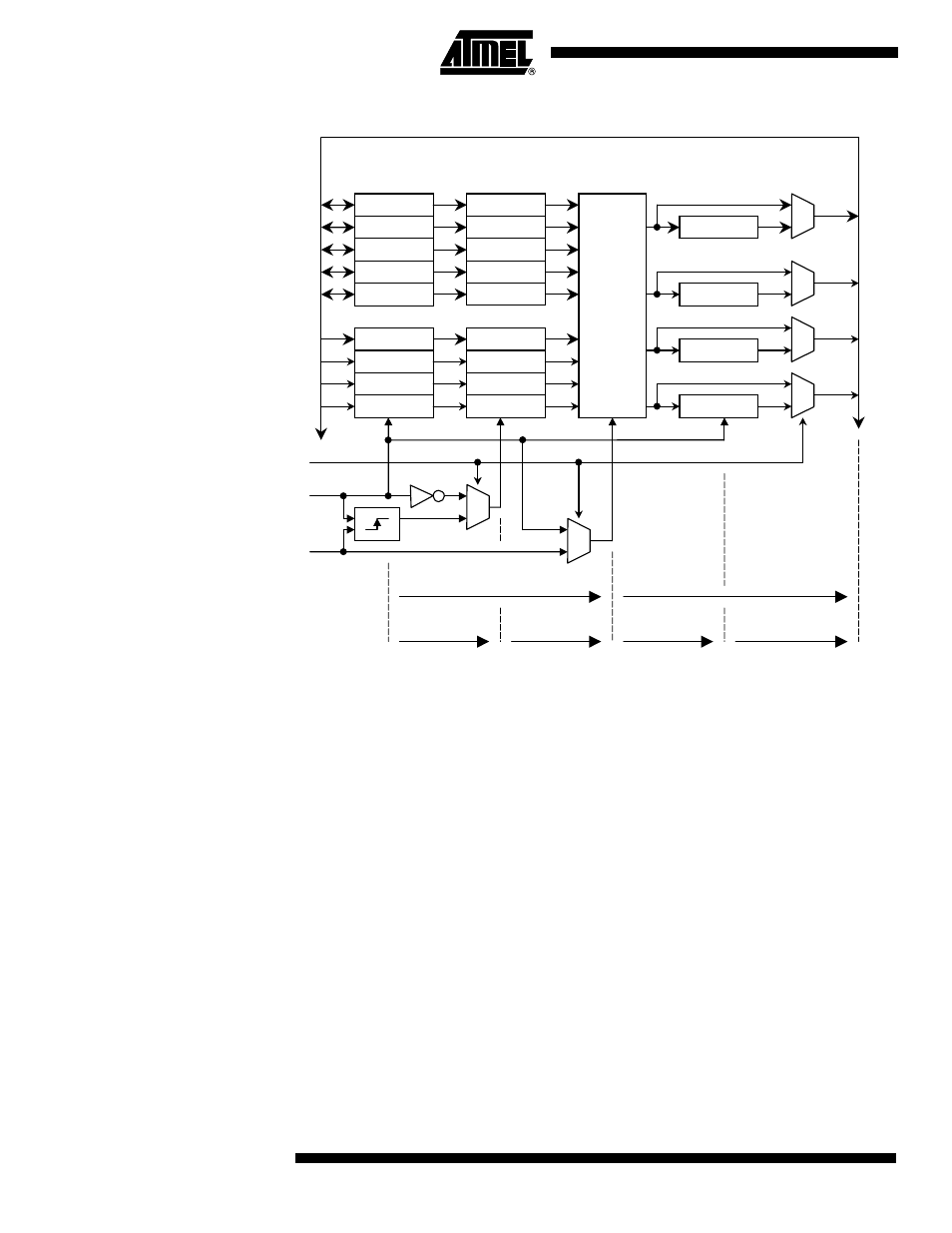

Figure 34. Timer/Counter1 Synchronization Register Block Diagram

Timer/Counter1 and the prescaler allow running the CPU from any clock source while

the prescaler is operating on the fast 64 MHz PCK clock in the asynchronous mode.

Note that the system clock frequency must be lower than one half of the PCK frequency.

Only when the system clock is generated from PCK dividing that by two, the ratio of the

PCK/system clock can be exactly two. The synchronization mechanism of the asynchro-

nous Timer/Counter1 needs at least two edges of the PCK when the system clock is

high. If the frequency of the system clock is too high, it is a risk that data or control val-

ues are lost.

The following Figure 35 shows the block diagram for Timer/Counter1.

OCR1A

8-BIT DATABUS

SYNC

MODE

1CK delay

TCNT1

CK

OCF1A

OCF1B

TCNT1

TOV1

OCR1B

OCR1C

TCCR1A

TCCR1B

OCR1A_SI

OCR1B_SI

OCR1C_SI

TCCR1A_SI

TCCR1B_SI

TCNT1

OCF1A

OCF1B

TOV1

TCNT1_SI

OCF1A_SI

OCF1B_SI

TOV1_SI

TCNT_SO

OCF1A_SO

OCF1B_SO

TOV1_SO

S

A

ASYNC

MODE

1PCK delay

1/2PCK -1CK delay

1/2PCK -1CK delay

PCK

PCKE

S

A

S

A

S

A

S

A

S

A

no delay

no delay

IO-registers

Input syncronization

registers

Timer/Counter1

Output

multiplexers

Output

syncronization

registers