External interrupt, Pin change interrupt, Attiny26(l) – Rainbow Electronics ATtiny26L User Manual

Page 38

38

ATtiny26(L)

1477B–AVR–04/02

External Interrupt

The External Interrupt is triggered by the INT0 pin. Observe that, if enabled, the interrupt

will trigger even if the INT0 pin is configured as an output. This feature provides a way of

generating a software interrupt. The External Interrupt can be triggered by a falling or

rising edge, a pin change, or a low level. This is set up as indicated in the specification

for the MCU Control Register – MCUCR. When the External Interrupt is enabled and is

configured as level triggered, the interrupt will trigger as long as the pin is held low.

Pin Change Interrupt

The pin change interrupt is triggered by any change on any I/O pin of Port B and pins

PA3, PA6, and PA7, if the interrupt is enabled and alternate function of the pin does not

mask out the interrupt. The bit PCIE1 in GIMSK enables interrupt from pins PB[7:4],

PA[7:6], and PA[3]. PCIE0 enables interrupt on digital pins PB[3:0].

The pin change interrupt is different from other interrupts in two ways. First, pin change

interrupt enable bits PCIE1 and PCIE0 also mask the flag if they are not set. The normal

operation on most interrupts is that the flag is always active and only the execution of

the interrupt is masked by the interrupt enable.

Secondly, please note that pin change interrupt is disabled for any pin that is configured

as an alternate function. For example, no pin change interrupt is generated from pins

that are configured as AREF, AIN0 or AIN1, OC1A, OC1A, OC1B, OC1B, XTAL1, or

XTAL2 in a fuse selected clock option, Timer0 clocking, or RESET function. See Table

17 for alternate functions which mask the pin change interrupt and how the function is

enabled. For example pin change interrupt on the PB0 is disabled when USI Two-wire

mode or USI Three-wire mode or Timer/Counter1 inverted output compare is enabled.

If the interrupt is enabled, the interrupt will trigger even if the changing pin is configured

as an output. This feature provides a way of generating a software interrupt. Also

observe that the pin change interrupt will trigger even if the pin activity triggers another

interrupt, for example the external interrupt. This implies that one external event might

cause several interrupts.

The value of the programmed fuse is “0” and unprogrammed is “1”. Each of the lines

enables the alternate function so “or” function of the lines enables the function.

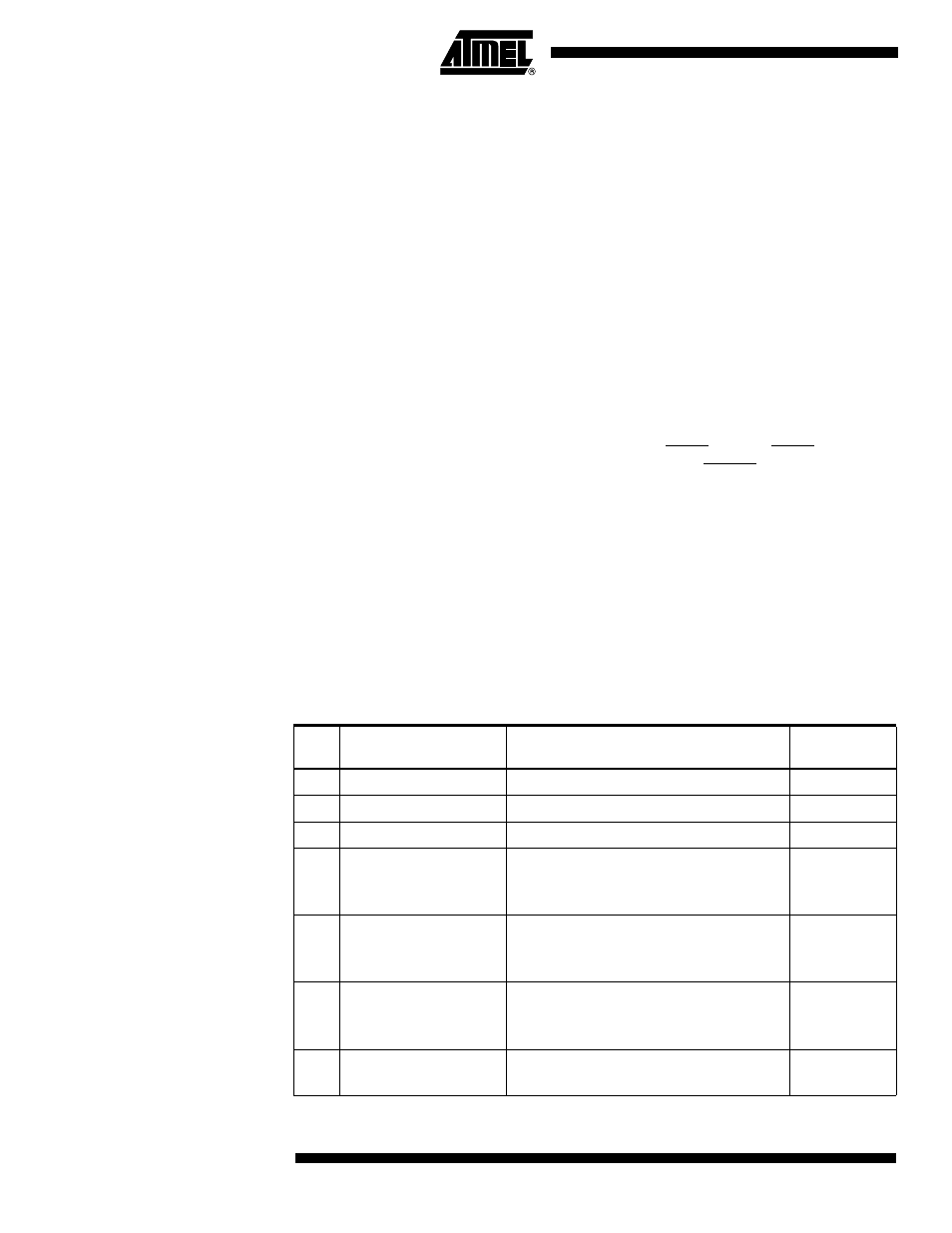

Table 17. Alternative Functions

Pin

Alternate Function

Control Register[Bit Name] which

set the Alternate Function

Bit or Fuse

Value

PA3

AREF

ADMUX[REFS0]

1

PA6

Analog Comparator

ACSR[ACD]

0

PA7

Analog Comparator

ACSR[ACD]

0

PB0

USI Two-wire mode

USI Three-wire mode

TC1 compare/PWM

USICR[USIWM1]

USICR[USIWM1,USIWM0]

TCCR1A[COM1A1,COM1A0,PWM1A]

1

01

011

PB1

USI Three-wire mode

TC1 compare/PWM

USICR[USIWM1,USIWM0]

TCCR1A[COM1A1]

TCCR1A[COM1A0]

01

1

1

PB2

USI Two-wire mode

USI Three-wire mode

TC1 compare/PWM

USICR[USIWM1]

USICR[USIWM1,USIWM0]

TCCR1A[COM1B1,COM1B0,PWM1B]

1

01

011

PB3

TC1 compare/PWM

TCCR1A[COM1B1]

TCCR1A[COM1B0]

1

1