Samsung S3F80JB User Manual

Page 83

CONTROL REGISTERS

S3F80JB

4-16

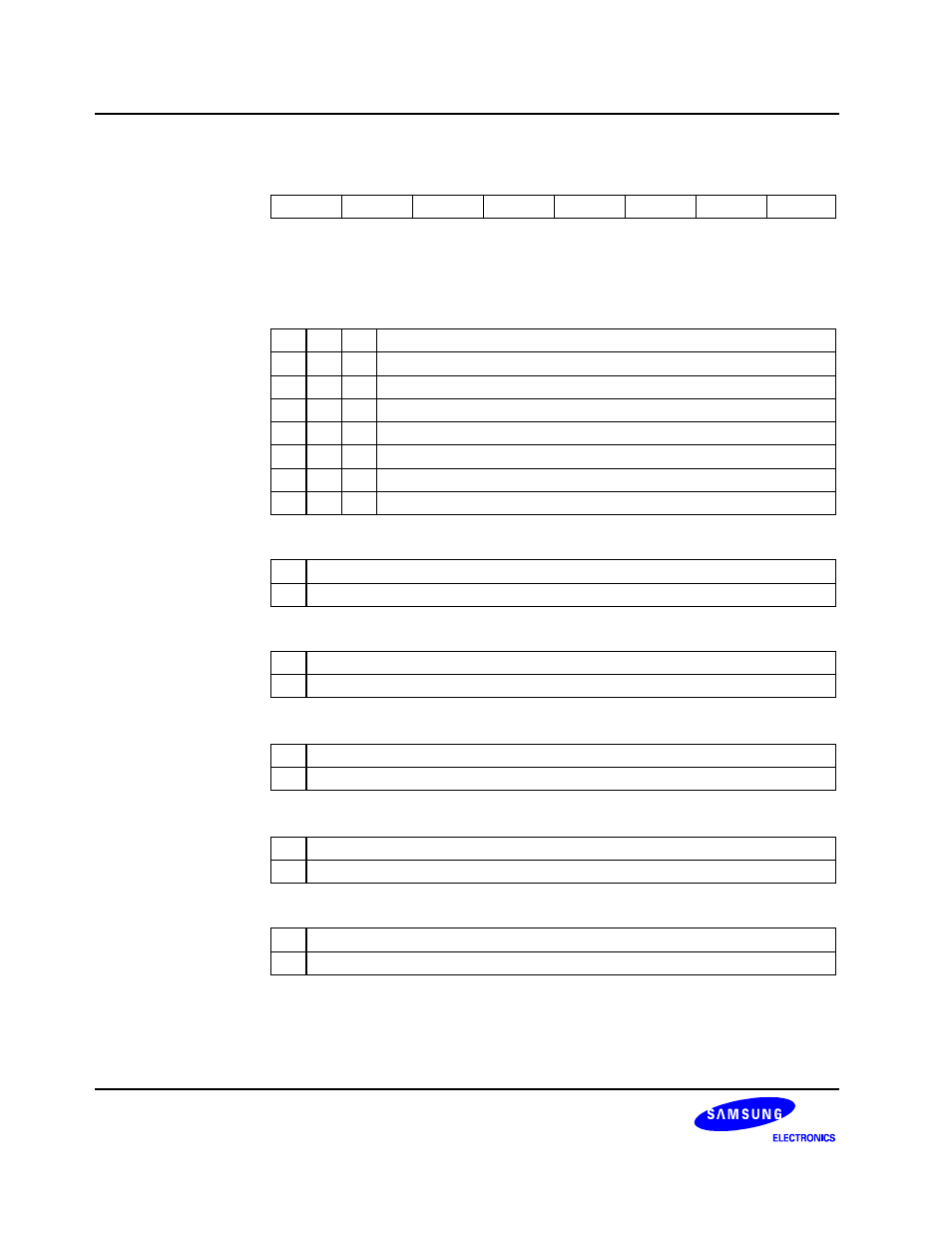

IPR

—

Interrupt

Priority

Register

FFH

Set1

Bank0

Bit

Identifier

.7 .6 .5 .4 .3 .2 .1 .0

Reset Value

x x x x x x x x

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

Addressing Mode

Register addressing mode only

.7, .4, and .1

Priority Control Bits for Interrupt Groups A, B, and C

0

0

0

Group

priority

undefined

0

0

1

B > C > A

0

1

0

A > B > C

0

1

1

B > A > C

1

0

0

C > A > B

1

0

1

C > B > A

1

1

0

A > C > B

1

1

1

Group

priority

undefined

.6

Interrupt Subgroup C Priority Control Bit

0

IRQ6 > IRQ7

1

IRQ7 > IRQ6

.5

Interrupt Group C Priority Control Bit

0

IRQ5 > (IRQ6, IRQ7)

1

(IRQ6, IRQ7) > IRQ5

.3

Interrupt Subgroup B Priority Control Bit

(See Note)

0 IRQ3>IRQ4

1 IRQ4>IRQ3

.2

Interrupt Group B Priority Control Bit

(See Note)

0 IRQ2

>(IRQ3,

IRQ4)

1

(IRQ3, IRQ4) > IRQ2

.0

Interrupt Group A Priority Control Bit

0

IRQ0 > IRQ1

1

IRQ1 > IRQ0

NOTE: The S3F80JB interrupt structure uses eight levels: IRQ0-IRQ7.