T1con – Samsung S3F80JB User Manual

Page 109

CONTROL REGISTERS

S3F80JB

4-42

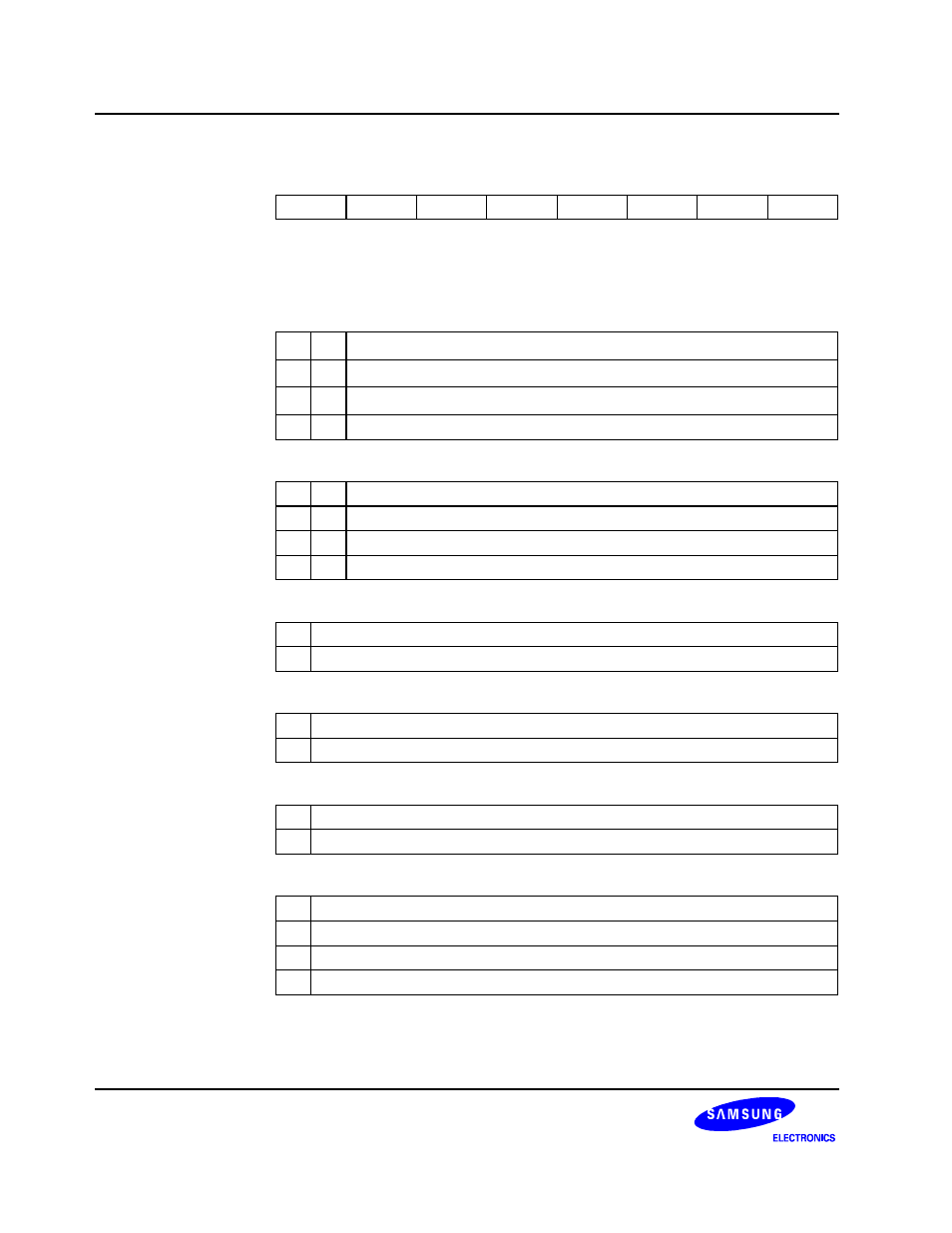

T1CON

— Timer 1 Control Register FAH

Set1

Bank0

Bit

Identifier

.7 .6 .5 .4 .3 .2 .1 .0

Reset Value

0 0 0 0 0 0 0 0

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

Addressing Mode

Register addressing mode only

.7 and .6

Timer 1 Input Clock Selection Bits

0 0

f

OSC

/4

0 1

f

OSC

/8

1 0

f

OSC

/16

1

1

Internal clock (counter A flip-flop, T-FF)

.5 and .4

Timer 1 Operating Mode Selection Bits

0

0

Interval timer mode (counter cleared by match signal)

0

1

Capture mode (rising edges, counter running, OVF can occur)

1

0

Capture mode (falling edges, counter running, OVF can occur)

1 1

Capture

mode

(rising and falling edges, counter running, OVF can occur)

.3

Timer 1 Counter Clear Bit

0 No

effect

(when

write)

1

Clear T1 counter, T1CNT (when write)

.2

Timer 1 Overflow Interrupt Enable Bit (note)

0 Disable

T1

overflow

interrupt

1

Enable T1 overflow interrupt

.1

Timer 1 Match/Capture Interrupt Enable Bit

0 Disable

T1

match/capture

interrupt

1 Enable

T1

match/capture

interrupt

.0

Timer 1 Match/Capture Interrupt Pending Flag Bit

0

No T1 match/capture interrupt pending (when read)

0

Clear T1 match/capture interrupt pending condition (when write)

1

T1 match/capture interrupt is pending (when read)

1 No

effect

(when

write)

NOTE: A timer 1 overflow interrupt pending condition is automatically cleared by hardware. However, the timer 1 match/

capture interrupt, IRQ1, vector F6H, must be cleared by the interrupt service routine (S/W).