Samsung S3F80JB User Manual

Page 142

INSTRUCTION SET

S3F80JB

6-14

ADC

— Add with carry

ADC

dst,src

Operation:

dst

← dst + src + c

The source operand, along with the setting of the carry flag, is added to the destination operand

and the sum is stored in the destination. The contents of the source are unaffected. Two's-

complement addition is performed. In multiple precision arithmetic, this instruction permits the

carry from the addition of low-order operands to be carried into the addition of high-order

operands.

Flags: C:

Set if there is a carry from the most significant bit of the result; cleared otherwise.

Z: Set if the result is "0"; cleared otherwise.

S: Set if the result is negative; cleared otherwise.

V: Set if arithmetic overflow occurs, that is, if both operands are of the same sign and the result

is of the opposite sign; cleared otherwise.

D: Always cleared to "0".

H: Set if there is a carry from the most significant bit of the low-order four bits of the result;

cleared otherwise.

Format:

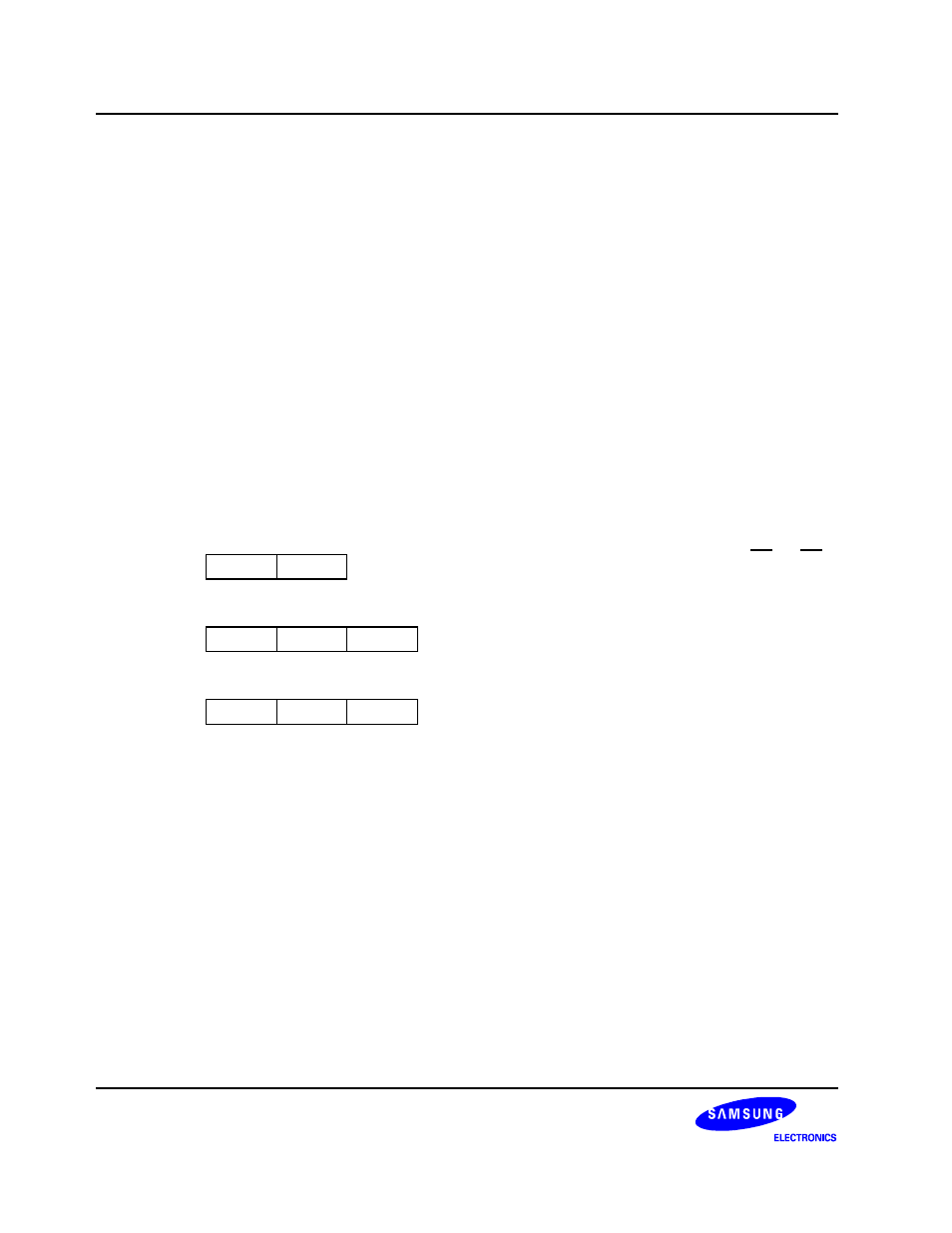

Bytes Cycles Opcode

(Hex)

Addr Mode

dst src

opc

dst | src

2 4 12 r

r

6 13

r

lr

opc src dst

3 6 14 R

R

6 15

R

IR

opc dst src

3 6 16 R

IM

Examples:

Given: R1 = 10H, R2 = 03H, C flag = "1", register 01H = 20H, register 02H = 03H, and

register 03H = 0AH:

ADC R1,R2

→

R1 = 14H, R2 = 03H

ADC R1,@R2

→

R1 = 1BH, R2 = 03H

ADC 01H,02H

→

Register 01H = 24H, register 02H = 03H

ADC 01H,@02H

→

Register 01H = 2BH, register 02H = 03H

ADC 01H,#11H

→

Register 01H = 32H

In the first example, destination register R1 contains the value 10H, the carry flag is set to "1",

and the source working register R2 contains the value 03H. The statement "ADC R1,R2" adds

03H and the carry flag value ("1") to the destination value 10H, leaving 14H in register R1.