Samsung S3F80JB User Manual

Page 124

INTERRUPT STRUCTURE

S3F80JB

5-14

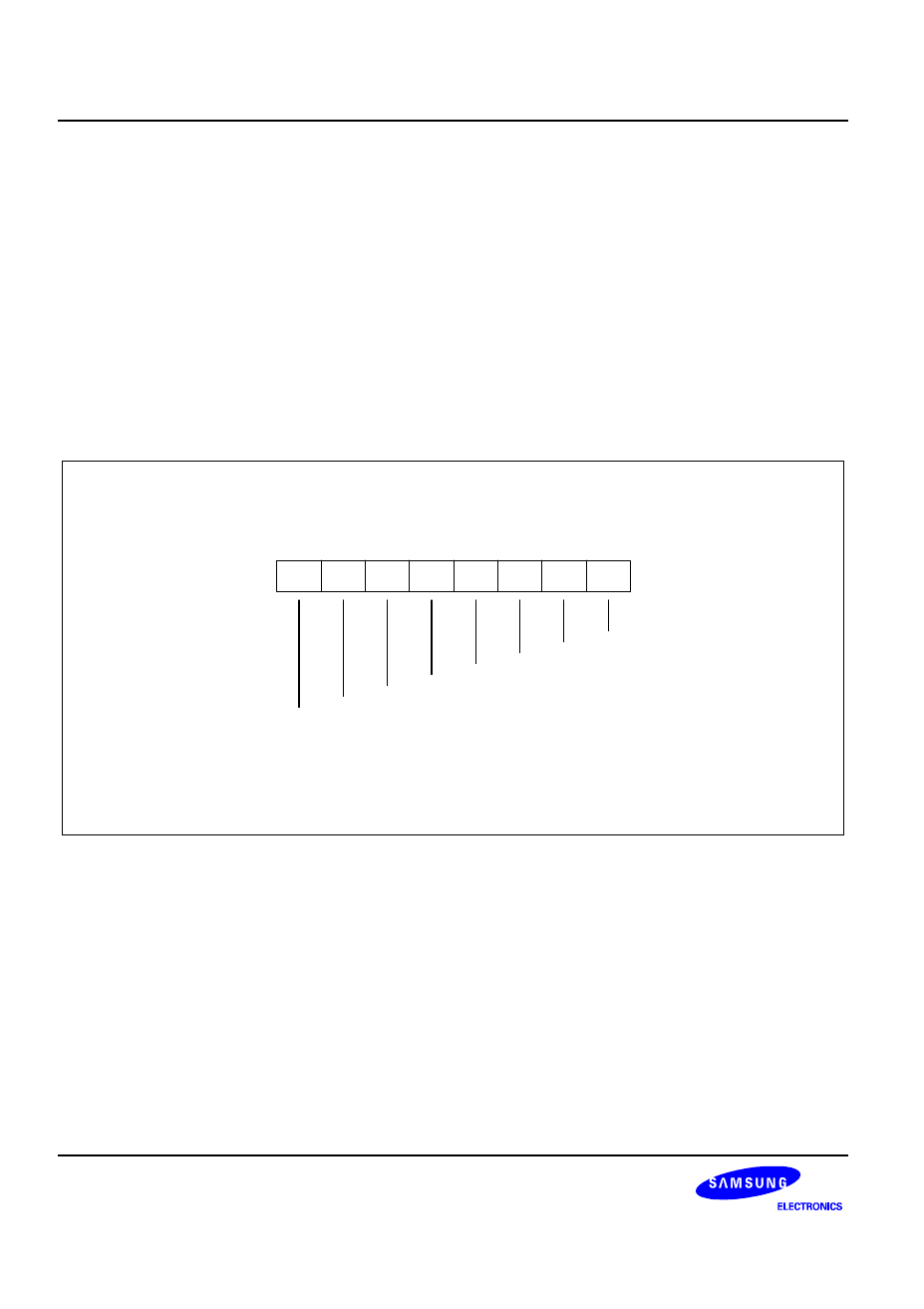

INTERRUPT REQUEST REGISTER (IRQ)

You can poll bit values in the interrupt request register, IRQ (DCH, Set 1, Bank0), to monitor interrupt request

status for all levels in the microcontroller’s interrupt structure. Each bit corresponds to the interrupt level of the

same number: bit 0 to IRQ0, bit 1 to IRQ1, and so on. A "0" indicates that no interrupt request is currently being

issued for that level; a "1" indicates that an interrupt request has been generated for that level.

IRQ bit values are read-only addressable using Register addressing mode. You can read (test) the contents of the

IRQ register at any time using bit or byte addressing to determine the current interrupt request status of specific

interrupt levels. After a reset, all IRQ status bits are cleared to “0”.

You can poll IRQ register values even if a DI instruction has been executed (that is, if global interrupt processing

is disabled). If an interrupt occurs while the interrupt structure is disabled, the CPU will not service it. You can,

however, still detect the interrupt request by polling the IRQ register. In this way, you can determine which events

occurred while the interrupt structure was globally disabled.

Interrupt Request Register (IRQ)

DCH, Set 1, Bank 0 , Read-only

.7

.6

.5

.4

.3

.2

.1

.0

MSB

LSB

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ0

Interrupt Level Request Enable Bits:

0 = Interrupt level is not pending

1 = Interrupt level is pending

Figure 5-9. Interrupt Request Register (IRQ)