Samsung S3F80JB User Manual

Page 25

S3F80JB

PRODUCT OVERVIEW

1-7

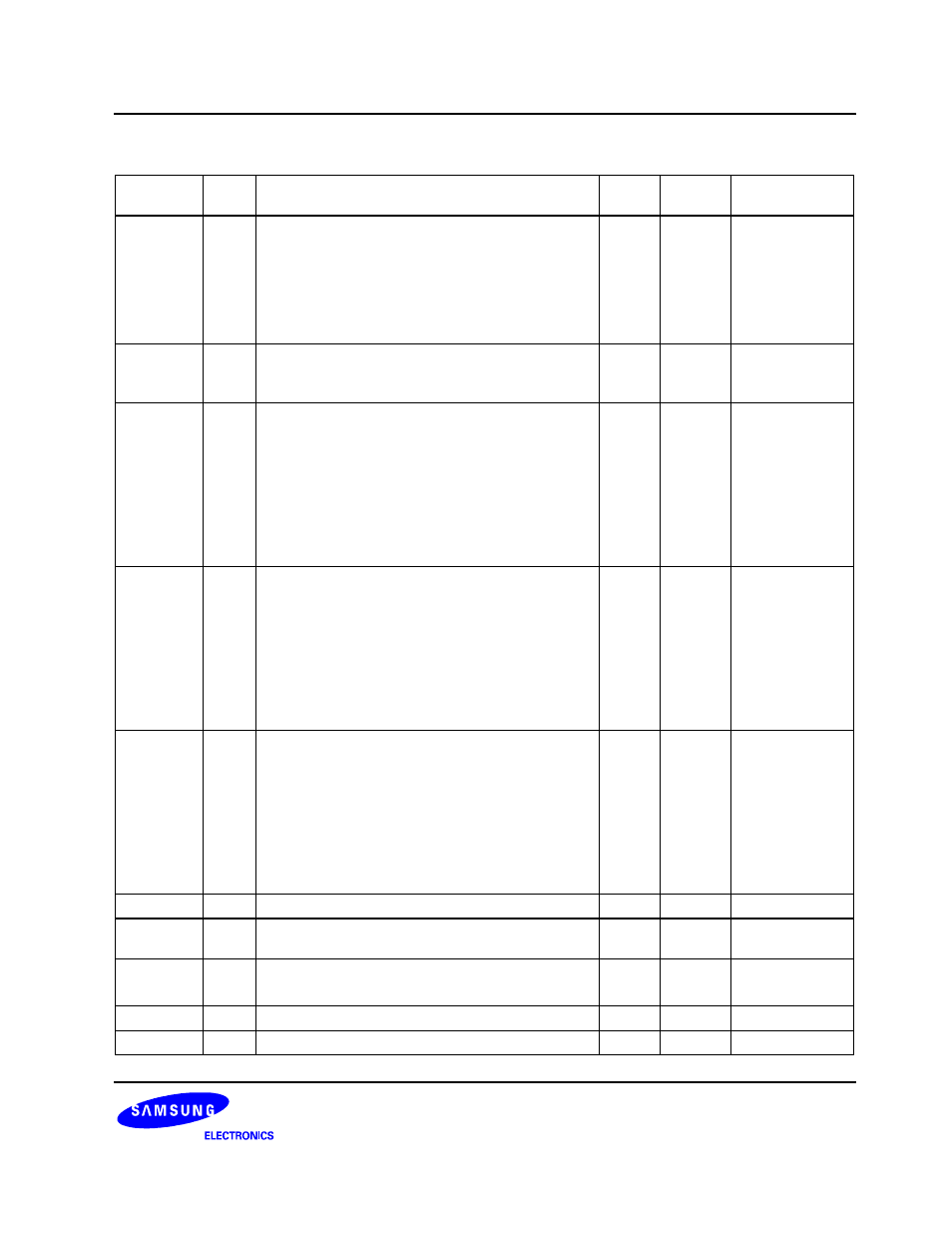

Table 1-1. Pin Descriptions of 32-SOP

Pin

Names

Pin

Type

Pin Description

Circuit

Type

32 Pin

No.

Shared

Functions

P0.0–P0.7

I/O

I/O port with bit-programmable pins. Configurable

to input or push-pull output mode. Pull-up resistors

are assignable by software. Pins can be assigned

individually as external interrupt inputs with noise

filters, interrupt enable/ disable, and interrupt

pending control. SED&R (note) circuit built in P0

for STOP releasing.

1 17–24 Ext.

INT

(INT0–INT3)

(INT4)

P1.0–P1.7

I/O

I/O port with bit-programmable pins. Configurable

to input mode or output mode. Pin circuits are

either push-pull or n-channel open-drain type.

2 9–16

–

P2.0–P2.3

P2.4–P2.7

I/O

I/O port with bit-programmable pins. Configurable

to input or push-pull output mode. Pull-up resistors

can be assigned by software. Pins can be

assigned individually as external interrupt inputs

with noise filters, interrupt enable/disable, and

interrupt pending control. SED & R (note) circuit

built in P2-P2.7 for STOP releasing. Also P2.4-

P2.7 can be assigned individually as analog input

pins for Comparator.

1

25–28

29,5,6,8

Ext. INT

(INT5–INT8)

(INT9)

(CIN0-CIN3)

P3.0

I/O

I/O port with bit-programmable pin. Configurable to

input mode, push-pull output mode, or n-channel

open-drain output mode. Input mode with a pull-up

resistor can be assigned by software.

This port 3 pin has high current drive capability.

Also P3.0 can be assigned individually as an

output pin for T0PWM or input pin for T0CAP.

In the tool mode, P3.0 is assigned as serial MTP

interface pin; SDAT

3 30

T0PWM/T0CAP

(SDAT)

P3.1

I/O

I/O port with bit-programmable pin. Configurable to

input mode, push-pull output mode, or n-channel

open-drain output mode. Input mode with a pull-up

resistor can be assigned by software.

This port 3 pin has high current drive capability.

Also P3.1 can be assigned individually as an

output pin for REM.

In the tool mode, P3.1 is assigned as serial MTP

interface pin; SCLK

4 31

REM

(SCLK)

X

OUT,

X

IN

–

System clock input and output pins

–

2,3

–

nRESET

I

System reset signal input pin and back-up mode

input.

6

7 –

TEST

I

Test signal input pin

(for factory use only; must be connected to V

SS

).

– 4

–

V

DD

–

Power supply input pin

– 32

–

V

SS

–

Ground pin

– 1

–