Samsung S3F80JB User Manual

Page 116

INTERRUPT STRUCTURE

S3F80JB

5-6

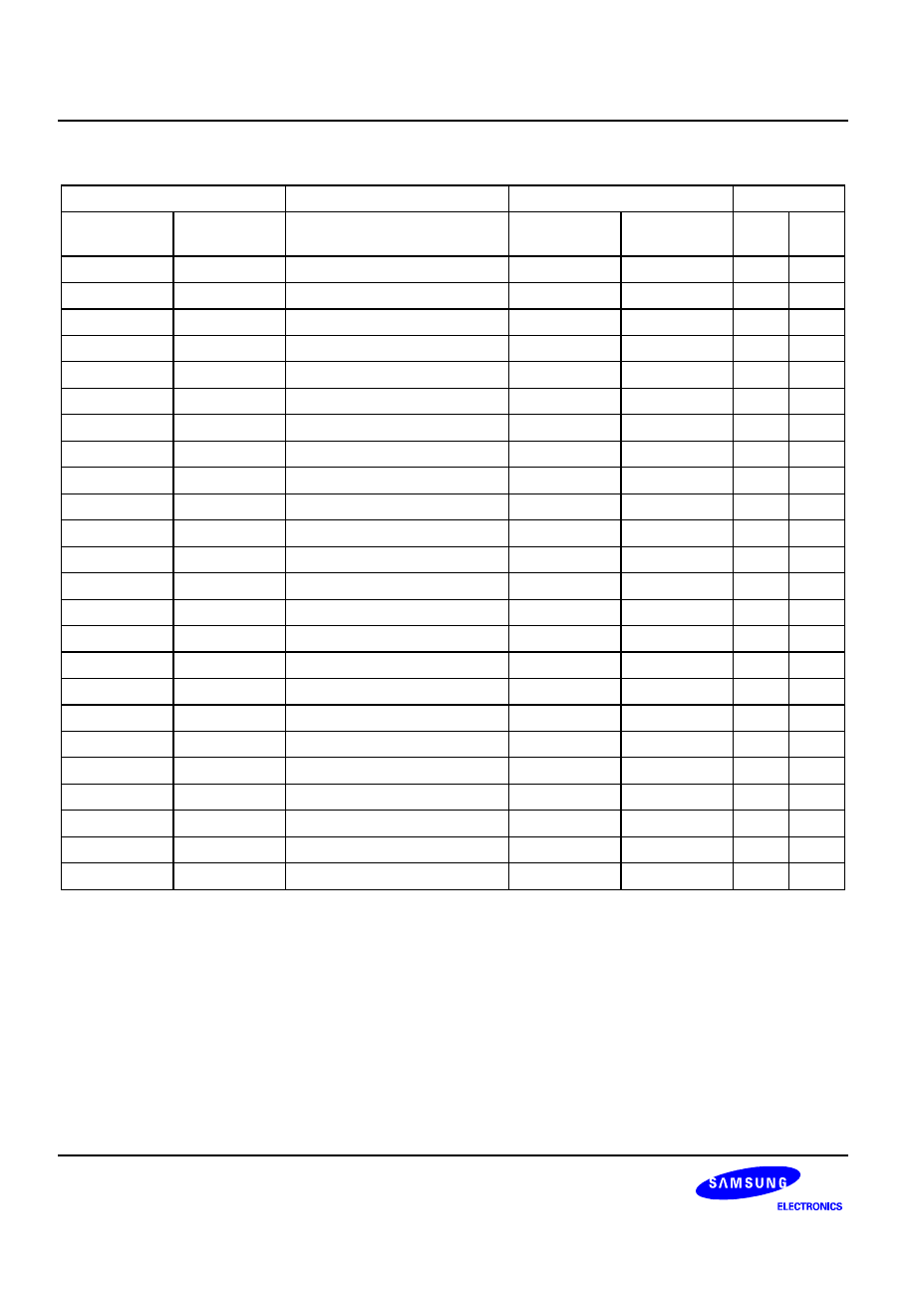

Table 5-1. S3F80JB Interrupt Vectors

Vector Address

Interrupt Source

Request

Reset/Clear

Decimal

Value

Hex

Value

Interrupt

Level

Priority in

Level

H/W

S/W

256

100H

Basic timer overflow/POR

RESET

–

√

252

FCH

Timer 0 match/capture

IRQ0

1

√

250

FAH

Timer 0 overflow

0

√

246

F6H

Timer 1 match/capture

IRQ1

1

√

244

F4H

Timer 1 overflow

0

√

236

ECH

Counter A

IRQ2

–

√

246

F2H

Timer 2 match/capture

IRQ3

1

√

244

F0H

Timer 2 overflow

0

√

232

E8H

P0.7 external interrupt

IRQ7

–

√

232

E8H

P0.6 external interrupt

–

√

232

E8H

P0.5 external interrupt

–

√

232

E8H

P0.4 external interrupt

–

√

230

E6H

P0.3 external interrupt

IRQ6

3

√

228

E4H

P0.2 external interrupt

2

√

226

E2H

P0.1 external interrupt

1

√

224

E0H

P0.0 external interrupt

0

√

216

D8H

P2.7 external interrupt

IRQ5

–

√

216

D8H

P2.6 external interrupt

–

√

216

D8H

P2.5 external interrupt

–

√

216

D8H

P2.4 external interrupt

–

√

214

D6H

P2.3 external interrupt

IRQ4

3

√

212

D4H

P2.2 external interrupt

2

√

210

D2H

P2.1 external interrupt

1

√

208

D0H

P2.0 external interrupt

0

√

NOTES:

1. Interrupt priorities are identified in inverse order: '0' is highest priority, '1' is the next highest, and so on.

2. If two or more interrupts within the same level content, the interrupt with the lowest vector address usually

has priority over one with a higher vector address. The priorities within a given level are fixed in hardware.

3. Reset (Basic timer overflow or POR) interrupt vector address can be changed by smart option

(Refer to Table 15-3 or Figure 2-2).