Samsung S3F80JB User Manual

Page 134

INSTRUCTION SET

S3F80JB

6-6

FLAGS REGISTER (FLAGS)

The flags register FLAGS contains eight bits that describe the current status of CPU operations. Four of these

bits, FLAGS.7–FLAGS.4, can be tested and used with conditional jump instructions; two others FLAGS.3 and

FLAGS.2 are used for BCD arithmetic.

The FLAGS register also contains a bit to indicate the status of fast interrupt processing (FLAGS.1) and a bank

address status bit (FLAGS.0) to indicate whether bank 0 or bank 1 is currently being addressed. FLAGS register

can be set or reset by instructions as long as its outcome does not affect the flags, such as, Load instruction.

Logical and Arithmetic instructions such as, AND, OR, XOR, ADD, and SUB can affect the Flags register. For

example, the AND instruction updates the Zero, Sign and Overflow flags based on the outcome of the AND

instruction. If the AND instruction uses the Flags register as the destination, then simultaneously, two write will

occur to the Flags register producing an unpredictable result.

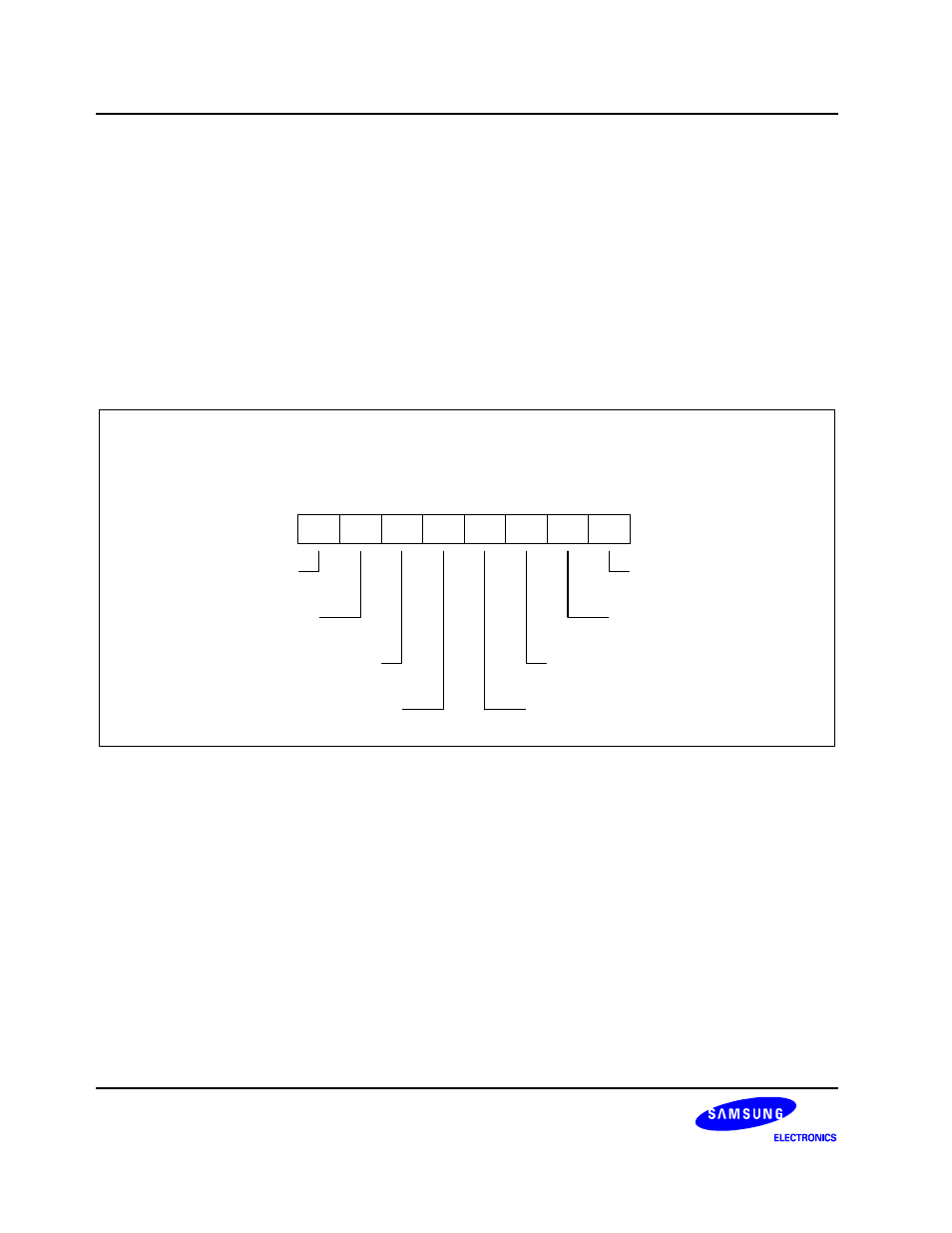

System Flags Register (FLAGS)

D5H, Set 1, Bank0 , R/W

.7

.6

.5

.4

.3

.2

.1

.0

MSB

LSB

Bank address

status flag (BA)

First interrupt

status flag (FIS)

Half-carry flag (H)

Decimal adjust flag (D)

Overflow (V)

Sign flag (S)

Zero flag (Z)

Carry flag (C)

Figure 6-1. System Flags Register (FLAGS)