Samsung S3F80JB User Manual

Page 223

S3F80JB

RESET

8-5

NOTES

1. IPOR / LVD Control Bit is one of smart option bits assigned address 03FH. User can enable / disable

LVD in the stop mode by manipulating this bit. When the value is ‘1’, LVD always operate in the

normal and stop mode. When the value is ‘0’, LVD is disabled in the stop mode. But, LVD is enabled

in the normal operating mode.

2. CPU can enter stop mode by setting STOPCON (Stop Control Register) into 0A5H before execution

STOP instruction.

3. This signal is output of IPOR/LVD Control Bit setting. So that is one of two cases; one is LVD enable

in STOP mode, the other is LVD disable in STOP mode.

4. This signal is output relating to STOP mode. If STOPCON has 0A5H, and STOP instruction is

executed, that output signal makes S3F80JB enter STOP mode. So that is one of two statuses; one is

STOP mode, the other is not STOP mode.

5. In S3F80JB, one between LVD and IPOR is selected as reset source by IPOR / LVD Control Bit

setting value of smart option in the stop mode. If the setting value is ‘0’, LVD can be disabled by

STOP instruction. Instead of LVD, IPOR is enabled. If the setting value is ‘1’, LVD is enabled

regardless of executing STOP instruction and IPOR is disabled.

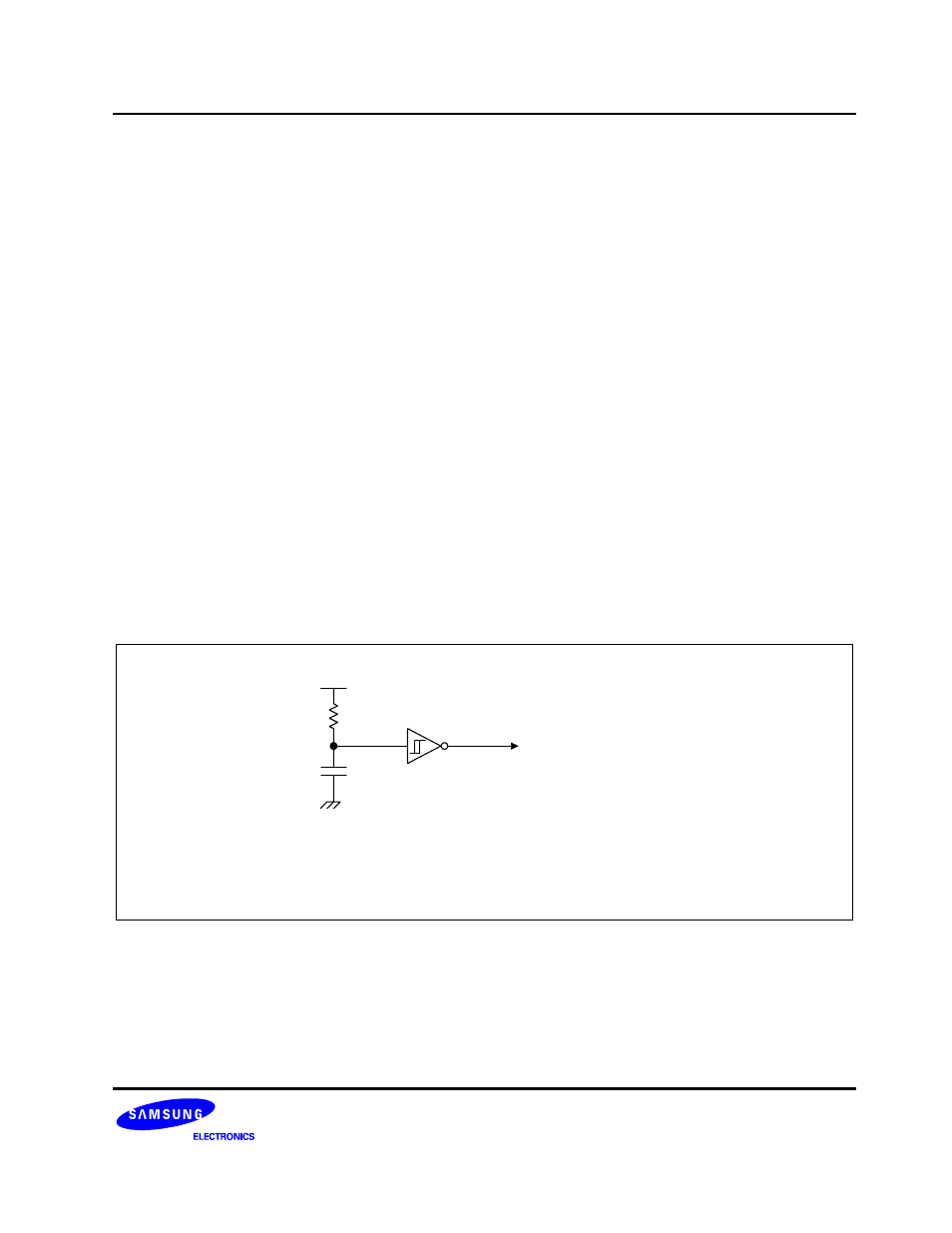

INTERNAL POWER-ON RESET

The power-on reset circuit is built on the S3F80JB product. During a power-on reset, the voltage at V

DD

goes to

high level and the schmitt-trigger input of POR circuit is forced to low level and then to high level. The power-on

reset circuit makes a reset signal whenever the power supply voltage is powering-up and the schmitt- trigger input

senses the low level. This on-chip POR circuit consists of an internal resistor, an internal capacitor, and a schmitt-

trigger input transistor. IPOR can be enabled by setting IPOR / LVD control bit of smart option to ‘0’.

V

DD

System Reset

C

Schmitt Trigger Inverter

V

SS

R: 3000k

Ω On-Chip Internal Resistor

C: 340pF On-Chip Internal Capacitor

Figure 8-4. Internal Power-On Reset Circuit