Intel NetStructure MPCBL0001 User Manual

Page 35

Technical Product Specification

35

Order #273817

Intel NetStructure

®

MPCBL0001 High Performance Single Board Computer

Contents

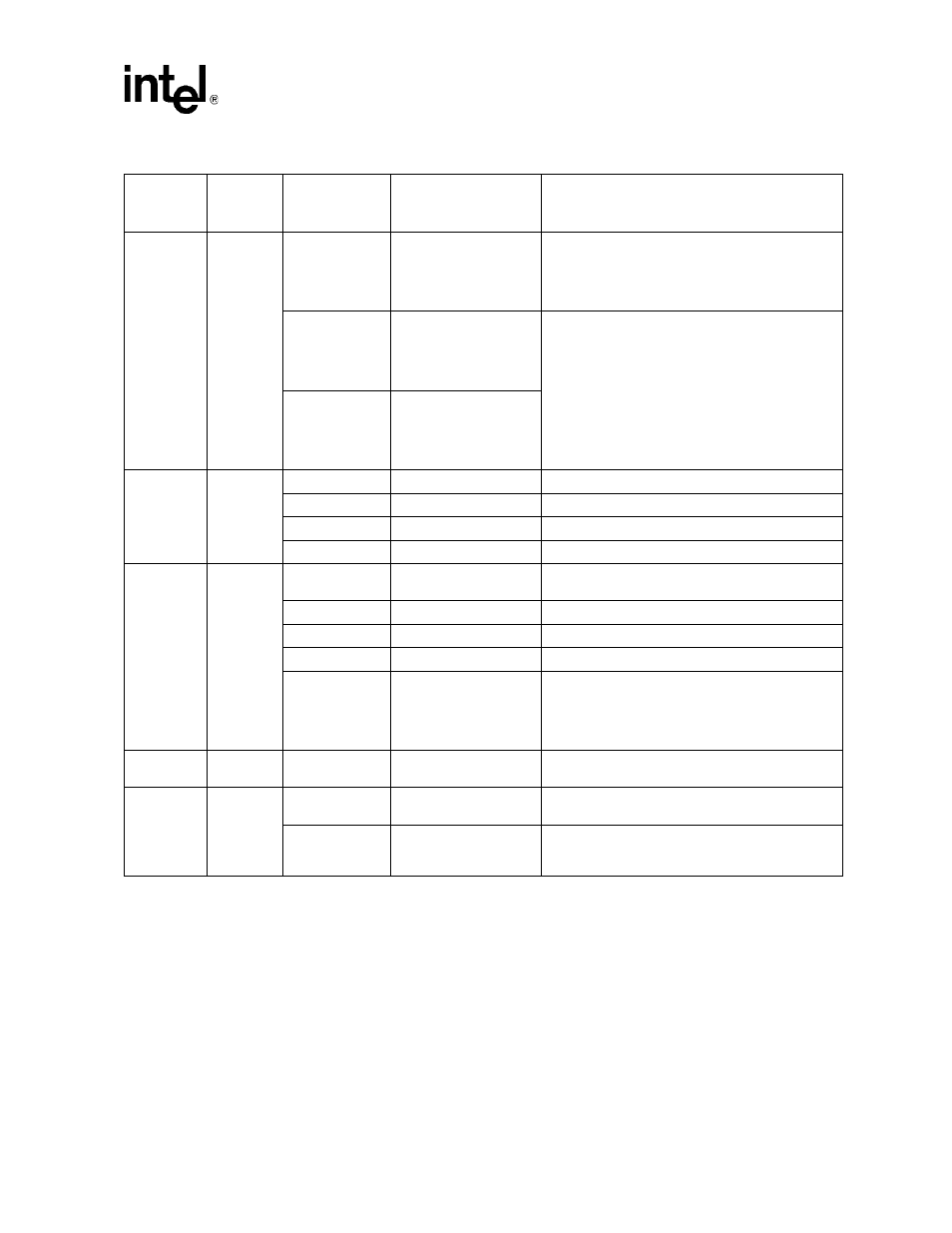

Critical

Interrupt

13h

04h

PCI PERR

Event data 2 = Bus No.

Event data 3:

Byte [7:3] = Device No

Byte [2:0] = Func. No

05h

PCI SERR

Event data 2 = Bus No.

Event data 3:

Byte [7:3] = Device No

Byte [2:0] = Func. No

07h

PCI Non-Fatal error

Event data 2 = Bus No.

Event data 3:

Byte [7:3] = Device No

Byte [2:0] = Func. No

System

ACPI Power

state

22h

00h

S0/G0

1

Board is running

06h

S4/S5

1

Soft-off

0Bh

Legacy ON state

1

Indicate ON for board that doesn’t support ACPI

0Ch

Legacy OFF state

1

Legacy soft-off

Watchdog

2

23h

00h

Timer expired, status

only

01h

Hard Reset

POST/Boot monitor timed out

02h

Power Down

OS WDT shutdown after the monitor timeout

03h

Power Cycle

OS WDT reset after the monitor timeout

08h

Timer Interrupt

Event data 2:

Byte [7:4] = Interrupt Type

0h = none

2h = NMI

Boot Error

1Eh

03h

Invalid Boot Sector

Event will be logged if the BIOS detects an invalid

boot sector.

SMI Timeout E0h

00h

State De-Asserted

1

This is the normal situation when a board is able to

power up.

01h

State Asserted

The SMI line has been constantly asserted for 10

seconds which indicates a severe hardware failure

around the CPU.

Table 3.

SEL Events Supported by the MPCBL0001 SBC (Sheet 3 of 4)

Sensor

Type

Sensor

Type Code

Sensor-Specific

Offset (Event

Data 1, Bit 0-3)

Event

Remarks

NOTE:

1. These sensor offsets do not generate events, but they are valid offsets when reading the sensor values.

2. Watchdog sensor refers to WDT#1 per

Section 3.13.1

.