Intel NetStructure MPCBL0001 User Manual

Page 34

34

Technical Product Specification

Order #273817

Intel NetStructure

®

MPCBL0001 High Performance Single Board Computer

Contents

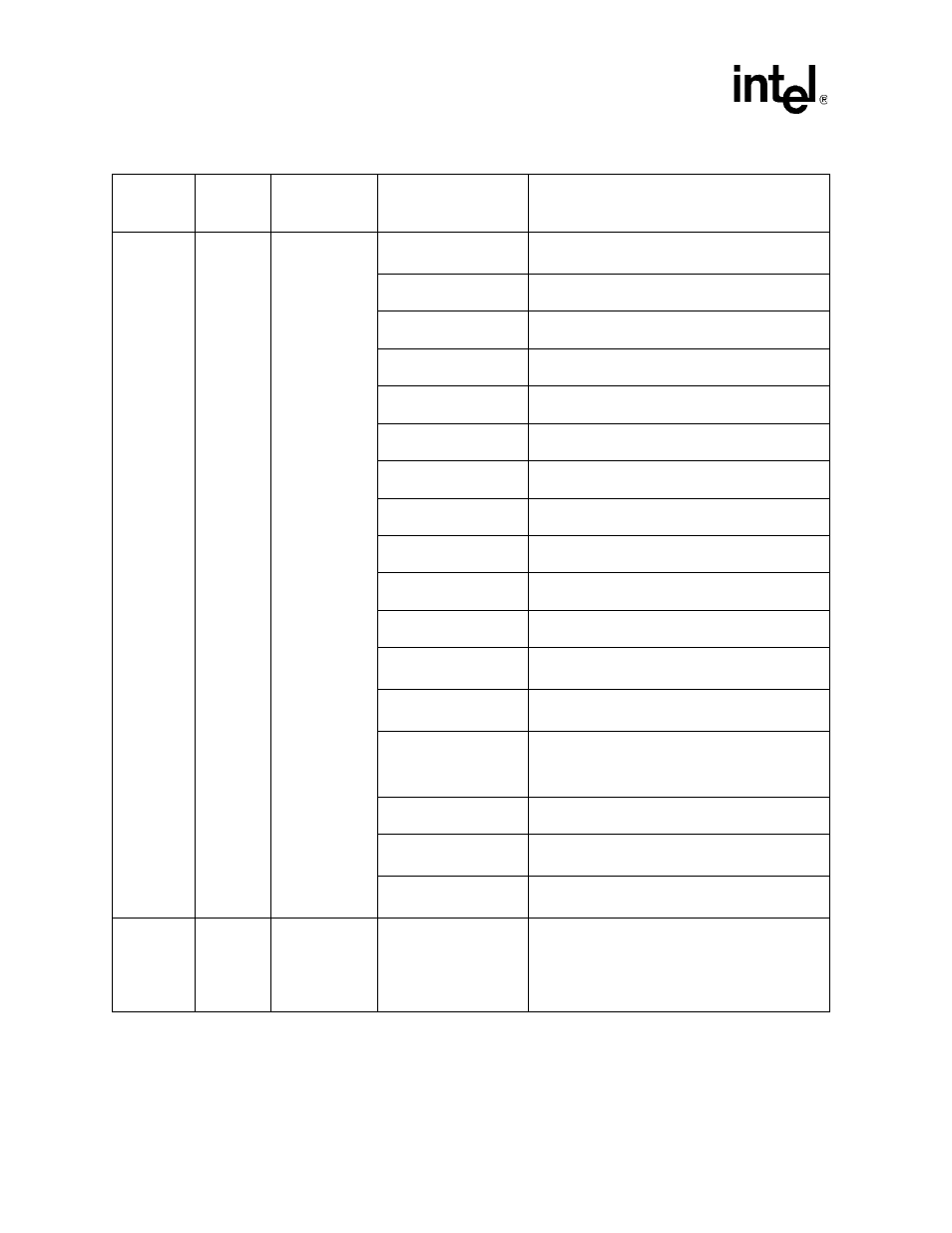

System

Firmware

Progress

0Fh

00h

BIOS checksum error

Event data 2 = 99h

Event data 3 = 99h

Timer Count Read/Write

error

Event data 2 = FEh

Event data 3 = 00h

CMOS Battery error

Event data 2 = FEh

Event data 3 = 01h

CMOS Diagnosis status

error

Event data 2 = FEh

Event data 3 = 02h

CMOS Checksum error

Event data 2 = FEh

Event data 3 = 03h

CMOS Memory Size

error

Event data 2 = FEh

Event data 3 = 04h

RAM Read/Write test

error

Event data 2 = FEh

Event data 3 = 05h

CMOS Date/Time error

Event data 2 = FEh

Event data 3 = 06h

Clear CMOS jumper

Event data 2 = FEh

Event data 3 = 07h

Clear Password Jumper

Event data 2 = FEh

Event data 3 = 08h

Manufacturing Jumper

Event data 2 = FEh

Event data 3 = 09h

Configuration error on

DIMM pair 0 (J8 & J9)

Event data 2 = FEh

Event data 3 = 10h

Configuration error on

DIMM pair 1(J10/J11)

Event data 2 = FEh

Event data 3 = 11h

No system memory is

physically installed or

fails to access any

DIMM's SPD data

Event data 2 = FEh

Event data 3 = 12h

BMC in update error

Event data 2 = FEh

Event data 3 = 0Ah

BMC Response Fail

error

Event data 2 = FEh

Event data 3 = 0Bh

Event Log Full error

Event data 2 = FEh

Event data 3 = 0Ch

Event

Logging

Disabled

10h

00h

Correctable Memory

Error Logging Disabled

Error Logging will be disabled after 10 events within

one hour.

Event data 2 = DIMM pair number

00 refers to J8/J9

01 refers to J10/J11

Table 3.

SEL Events Supported by the MPCBL0001 SBC (Sheet 2 of 4)

Sensor

Type

Sensor

Type Code

Sensor-Specific

Offset (Event

Data 1, Bit 0-3)

Event

Remarks

NOTE:

1. These sensor offsets do not generate events, but they are valid offsets when reading the sensor values.

2. Watchdog sensor refers to WDT#1 per

Section 3.13.1

.