1 reserved—bits 15–8, 2 gpio c6 (c6)—bit 7, 3 gpioc5 (c5)—bit 6 – Freescale Semiconductor 56F8122 User Manual

Page 86: This bit selects the alternate function for gpioc6, This bit selects the alternate function for gpioc5, 0 = tc0 (default) • 1 = txd0, 0 = tc1 (default) • 1 = rxd0

56F8322 Techncial Data, Rev. 10.0

86

Freescale Semiconductor

Preliminary

Note: PWM is NOT available in the 56F8122 device.

, the GPIO has the final control over which pin controls the I/O. SIM_GPS simply

decides which peripheral will be routed to the I/O.

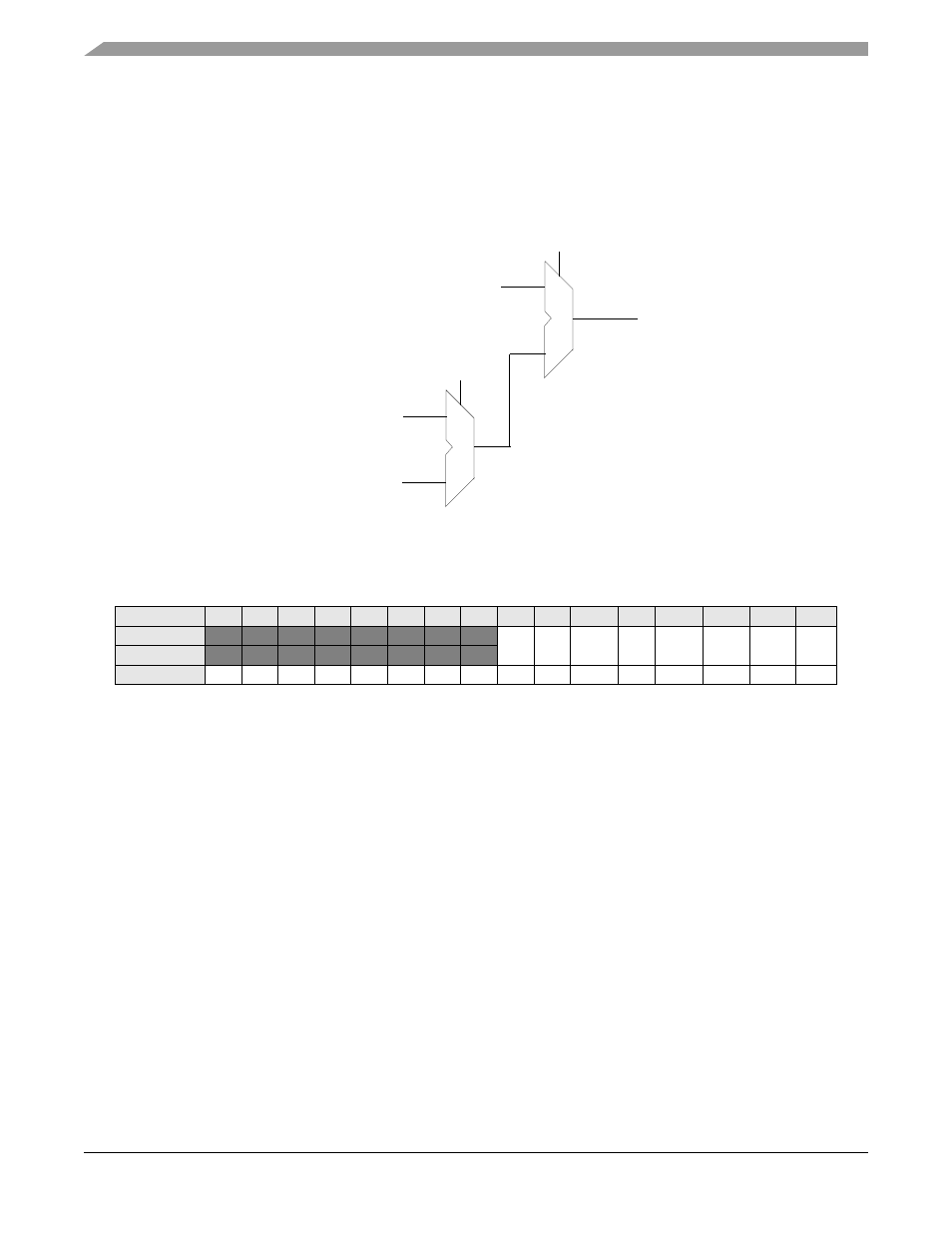

Figure 6-10 Overall Control of Pads Using SIM_GPS Control

Figure 6-11 GPIO Peripheral Select Register (SIM_GPS)

6.5.8.1

Reserved—Bits 15–8

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

6.5.8.2

GPIO C6 (C6)—Bit 7

This bit selects the alternate function for GPIOC6.

•

0 = TC0 (default)

•

1 = TXD0

6.5.8.3

GPIOC5 (C5)—Bit 6

This bit selects the alternate function for GPIOC5.

•

0 = TC1 (default)

•

1 = RXD0

Base + $B

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Read

0

0

0

0

0

0

0

0

C6

C5

B1

B0

A5

A4

A3

A2

Write

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GPIOX_PER Register

GPIO Controlled

I/O

Pad Control

SIM_GPS Register

Quad Timer Controlled

SCI Controlled

0

1

0

1