5 registers, Figure 3-4 internal clock operation – Freescale Semiconductor 56F8122 User Manual

Page 29

Registers

56F8322 Technical Data, Rev. 10.0

Freescale Semiconductor

29

Preliminary

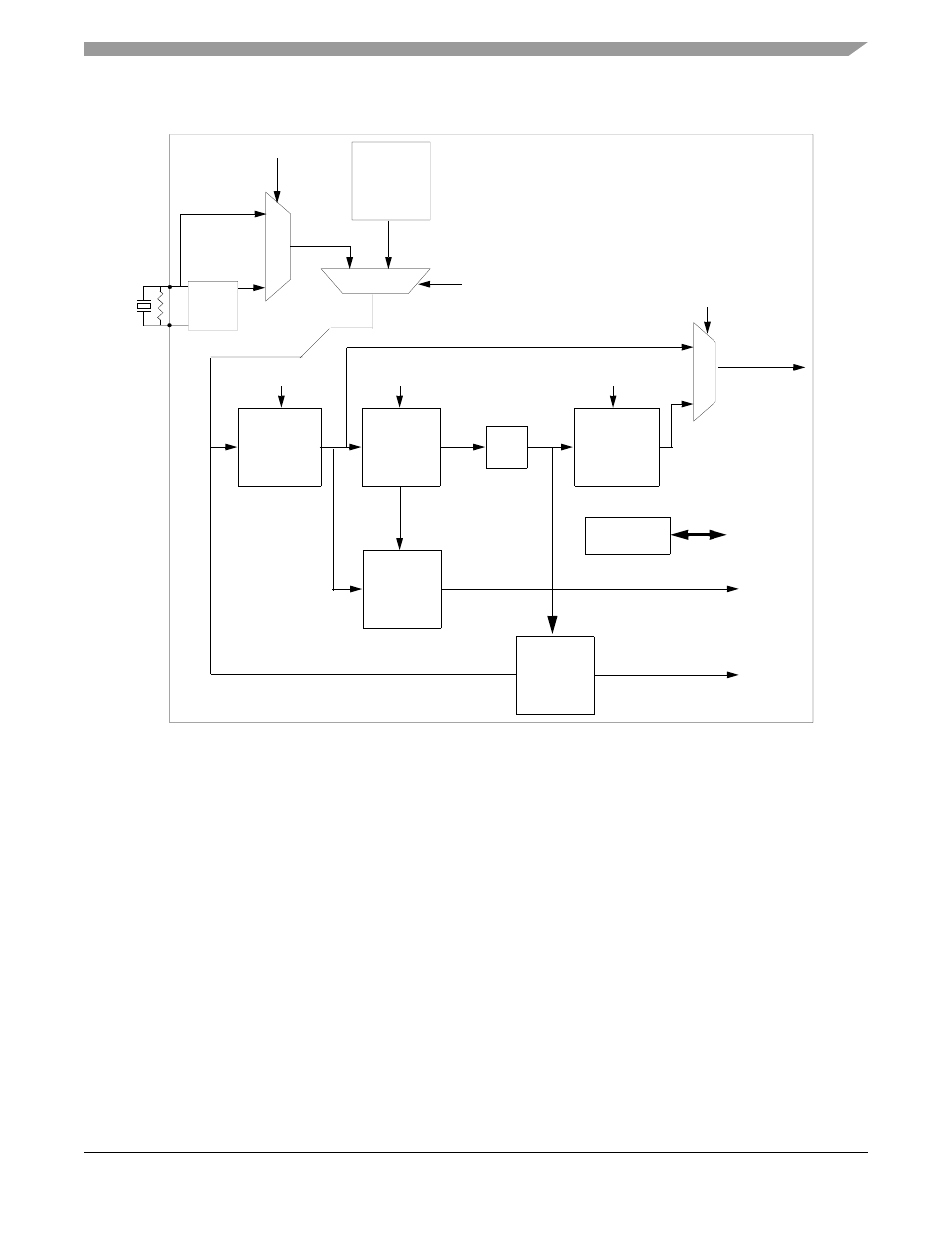

Figure 3-4 Internal Clock Operation

3.5 Registers

When referring to the register definitions for the OCCS in the 56F8300 Peripheral User Manual, use the

register definitions with the internal Relaxation Oscillator, since the 56F8322 and 56F8122 contain this

oscillator.

Crystal

OSC

Relaxation

OSC

CLK_MODE

XTAL

EXTAL

MUX

MUX

PRECS

PLLCID

PLL

x (1 to 128)

Postscaler

ч

(1, 2, 4, 8)

ч

2

Prescaler

÷

(1, 2, 4, 8)

Lock

Detector

Loss of

Reference

Clock

Detector

MUX

SYS_CLK2

source to the

SIM

Postscaler CLK

PLLDB

PLLCOD

LCK

Bus Interface

& Control

Bus

Interface

FREF

FEEDB

A

CK

loss of reference

clock interrupt

MS

TR

_

O

S

C

F

OUT

F

OUT

/2

ZSRC

This manual is related to the following products: