Freescale Semiconductor 56F8122 User Manual

Page 116

56F8322 Techncial Data, Rev. 10.0

116

Freescale Semiconductor

Preliminary

1

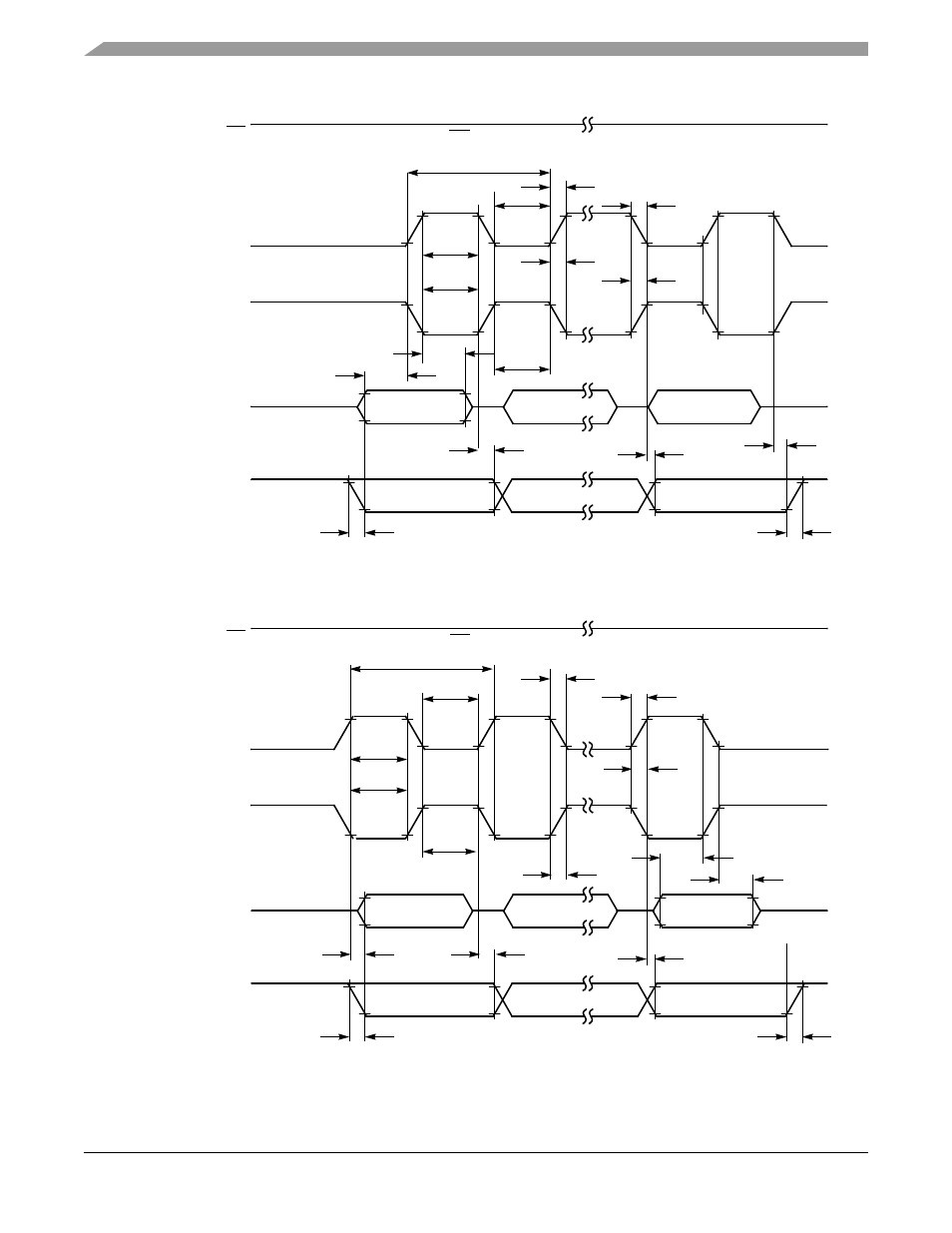

Figure 10-9 SPI Master Timing (CPHA = 0)

Figure 10-10 SPI Master Timing (CPHA = 1)

SCLK (CPOL = 0)

(Output)

SCLK (CPOL = 1)

(Output)

MISO

(Input)

MOSI

(Output)

MSB in

Bits 14–1

LSB in

t

F

t

C

t

CL

t

CL

t

R

t

R

t

F

t

DS

t

DH

t

CH

t

DI

t

DV

t

DI

(ref)

t

R

Master MSB out

Bits 14–1

Master LSB out

SS

(Input)

t

CH

SS is held High on master

t

F

SCLK (CPOL = 0)

(Output)

SCLK (CPOL = 1)

(Output)

MISO

(Input)

MOSI

(Output)

MSB in

Bits 14–1

LSB in

t

R

t

C

t

CL

t

CL

t

F

t

CH

t

DV

(ref)

t

DV

t

DI

(ref)

t

R

t

F

Master MSB out

Bits 14– 1

Master LSB out

SS

(Input)

t

CH

SS is held High on master

t

DS

t

DH

t

DI

t

R

t

F

This manual is related to the following products: