Figure 1-1 – Freescale Semiconductor 56F8122 User Manual

Page 10

56F8322 Techncial Data, Rev. 10.0

10

Freescale Semiconductor

Preliminary

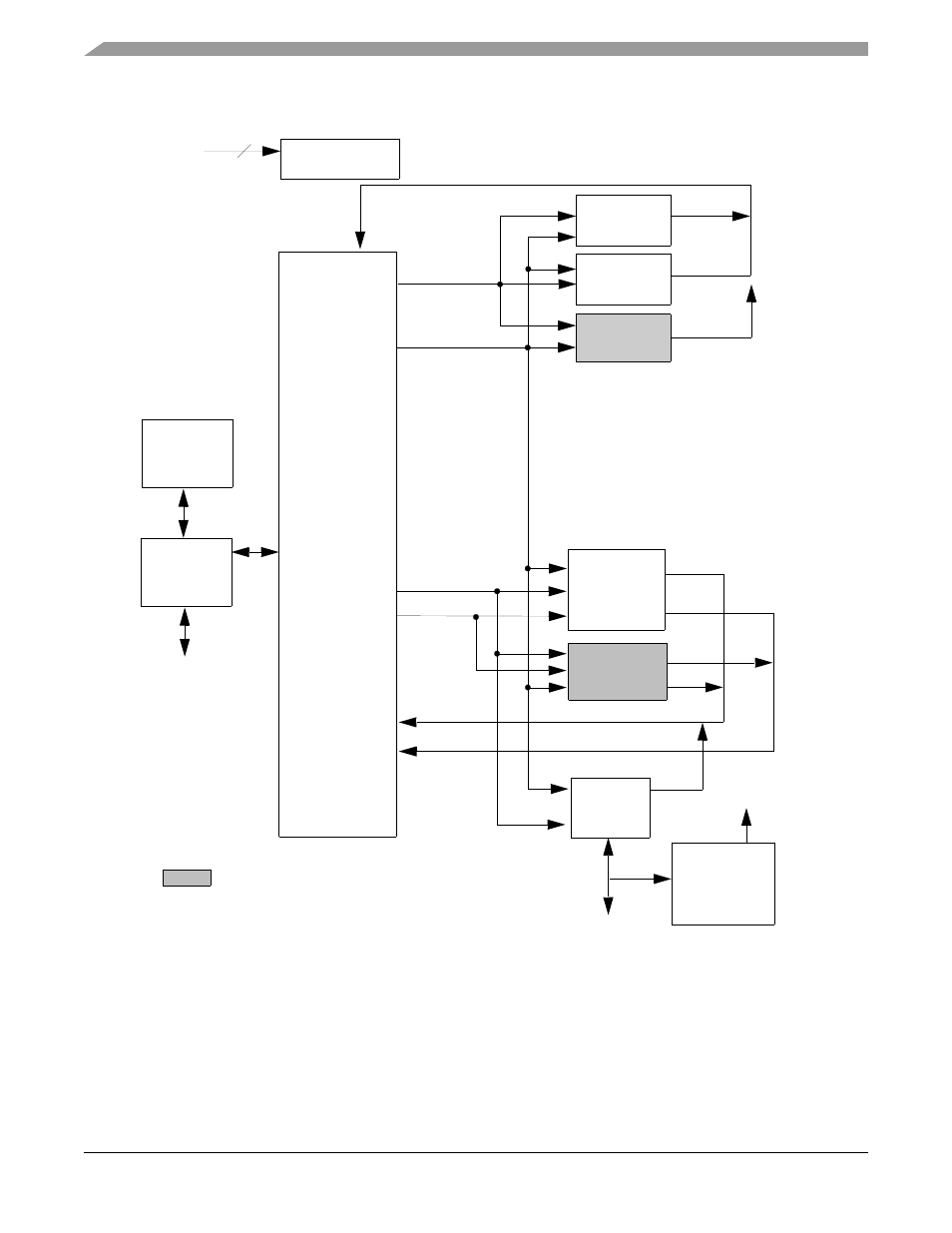

Figure 1-1 System Bus Interfaces

Note:

Flash memories are encapsulated within the Flash Memory Module (FM). Flash control is

accomplished by the I/O to the FM over the peripheral bus, while reads and writes are completed

between the core and the Flash memories.

Note:

The primary data RAM port is 32 bits wide. Other data ports are

16 bits.

56800E

Program

Flash

Program

RAM

Data RAM

Data

Flash

IPBus

Bridge

Boot

Flash

Flash

Memory

Module

CHIP

TAP

Controller

TAP

Linking

Module

4

Not available on the 56F8122 device.

JTAG / EOnCE

pdb_m[15:0]

pab[20:0]

cdbw[31:0]

xab1[23:0]

xab2[23:0]

xdb2_m[15:0]

cdbr_m[31:0]

IPBus

To Flash

Control Logic

External

JTAG Port

This manual is related to the following products: