Freescale Semiconductor 56F8122 User Manual

Page 37

Peripheral Memory Mapped Registers

56F8322 Technical Data, Rev. 10.0

Freescale Semiconductor

37

Preliminary

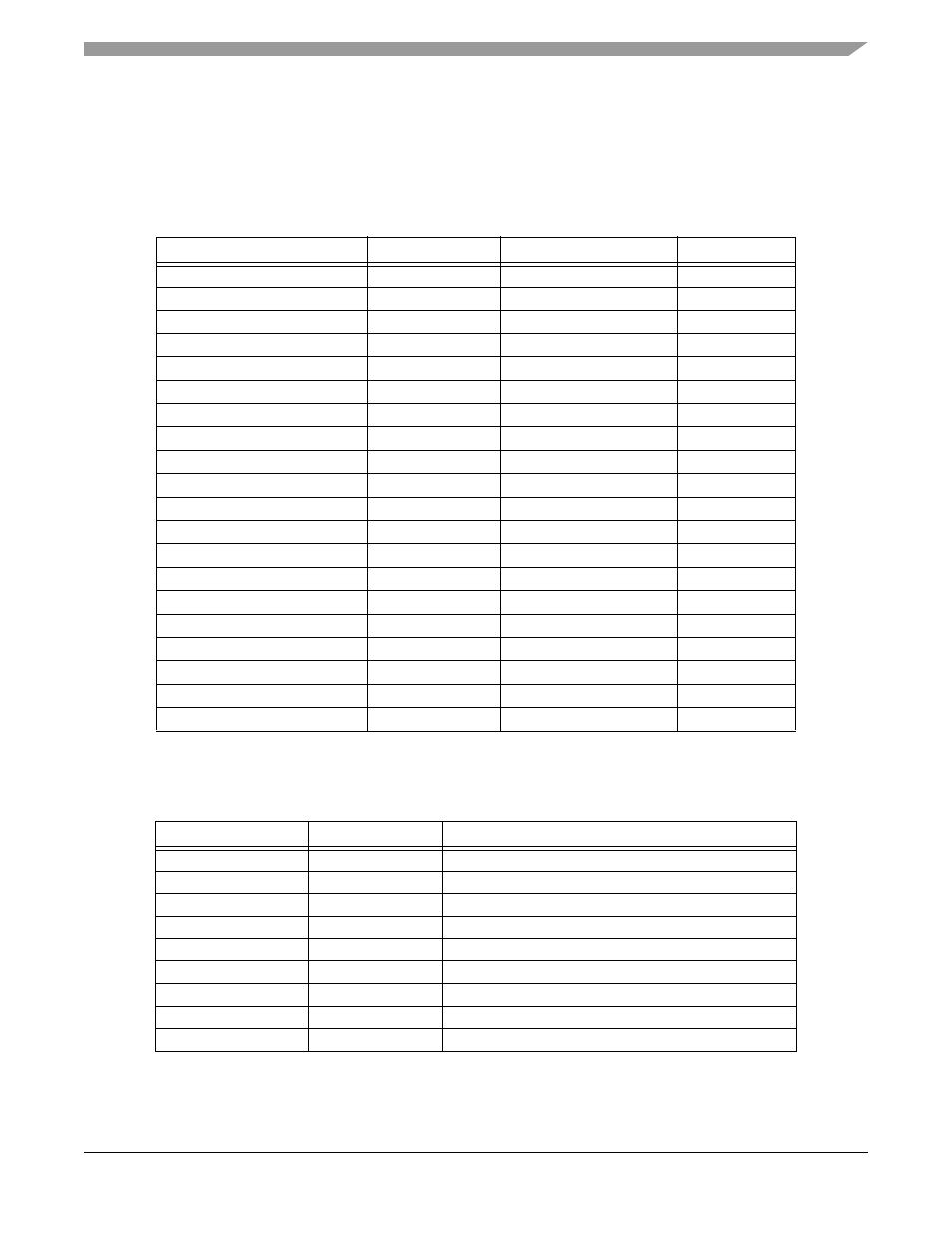

The following tables list all of the peripheral registers required to control or access the peripherals.

Note: Features in italics are NOT available on the 56F8122 device.

Table 4-7 Data Memory Peripheral Base Address Map Summary

Peripheral

Prefix

Base Address

Table Number

Timer A

TMRA

X:$00 F040

Timer C

TMRC

X:$00 F0C0

PWM A

PWMA

X:$00 F140

Quadrature Decoder 0

DEC0

X:$00 F180

ITCN

ITCN

X:$00 F1A0

ADC A

ADCA

X:$00 F200

Temperature Sensor

TSENSOR

X:$00 F270

SCI #0

SCI0

X:$00 F280

SCI #1

SCI1

X:$00 F290

SPI #0

SPI0

X:$00 F2A0

SPI #1

SPI1

X:$00 F2B0

COP

COP

X:$00 F2C0

PLL, OSC

CLKGEN

X:$00 F2D0

GPIO Port A

GPIOA

X:$00 F2E0

GPIO Port B

GPIOB

X:$00 F300

GPIO Port C

GPIOC

X:$00 F310

SIM

SIM

X:$00 F350

Power Supervisor

LVI

X:$00 F360

FM

FM

X:$00 F400

FlexCAN

FC

X:$00 F800

Table 4-8 Quad Timer A Registers Address Map

(TMRA_BASE = $00 F040)

Register Acronym

Address Offset

Register Description

TMRA0_CMP1

$0

Compare Register 1

TMRA0_CMP2

$1

Compare Register 2

TMRA0_CAP

$2

Capture Register

TMRA0_LOAD

$3

Load Register

TMRA0_HOLD

$4

Hold Register

TMRA0_CNTR

$5

Counter Register

TMRA0_CTRL

$6

Control Register

TMRA0_SCR

$7

Status and Control Register

TMRA0_CMPLD1

$8

Comparator Load Register 1