Freescale Semiconductor 56F8122 User Manual

Page 25

Signal Pins

56F8322 Technical Data, Rev. 10.0

Freescale Semiconductor

25

Preliminary

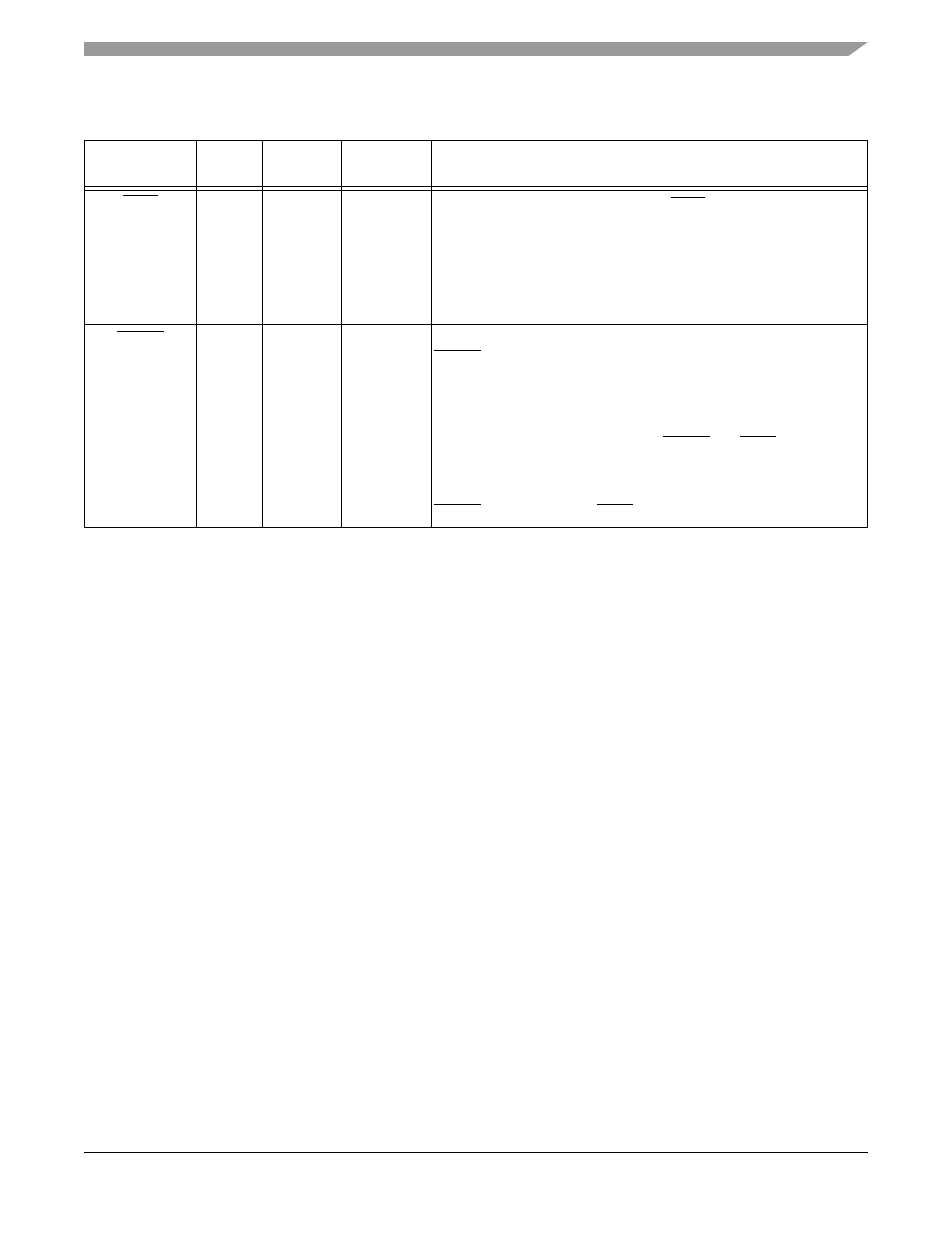

IRQA

(V

PP

)

11

Schmitt

Input

Input

N/A

External Interrupt Request A — The IRQA input is an asynchronous

external interrupt request during Stop and Wait mode operation.

During other operating modes, it is a synchronized external interrupt

request which indicates an external device is requesting service. It

can be programmed to be level-sensitive or negative-edge-triggered.

V

PP

— This pin is used for Flash debugging purposes.

RESET

2

Schmitt

Input

Input

Reset — This input is a direct hardware reset on the processor. When

RESET is asserted low, the hybrid controller is initialized and placed

in the reset state. A Schmitt trigger input is used for noise immunity.

The internal reset signal will be deasserted synchronous with the

internal clocks after a fixed number of internal clocks.

To ensure complete hardware reset, RESET and TRST should be

asserted together. The only exception occurs in a debugging

environment when a hardware DSP reset is required and it is

necessary not to reset the JTAG/EOnCE module. In this case, assert

RESET, but do not assert TRST.

Table 2-2 Signal and Package Information for the 48-Pin LQFP

Signal Name

Pin No.

Type

State During

Reset

Signal Description