Freescale Semiconductor 56F8122 User Manual

Page 47

Peripheral Memory Mapped Registers

56F8322 Technical Data, Rev. 10.0

Freescale Semiconductor

47

Preliminary

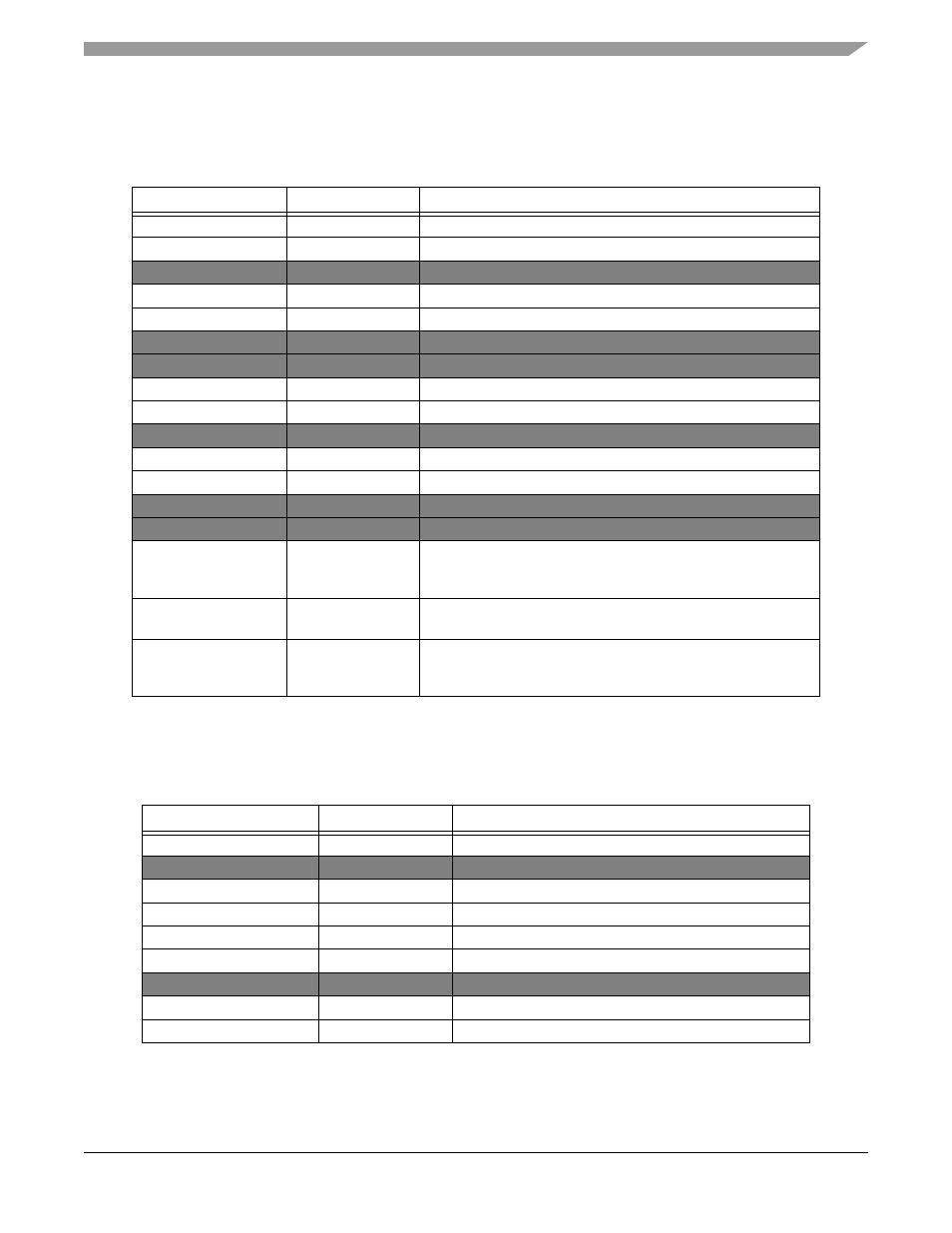

Table 4-26 Flash Module Registers Address Map

(FM_BASE = $00 F400)

Register Acronym

Address Offset

Register Description

FMCLKD

$0

Clock Divider Register

FMMCR

$1

Module Control Register

Reserved

FMSECH

$3

Security High Half Register

FMSECL

$4

Security Low Half Register

Reserved

Reserved

FMPROT

$10

Protection Register (Banked)

FMPROTB

$11

Protection Boot Register (Banked)

Reserved

FMUSTAT

$13

User Status Register (Banked)

FMCMD

$14

Command Register (Banked)

Reserved

Reserved

FMOPT 0

$1A

16-Bit Information Option Register 0

Hot temperature ADC reading of Temperature Sensor; value

set during factory test

FMOPT 1

$1B

16-Bit Information Option Register 1

Trim cap setting of the relaxation oscillator

FMOPT 2

$1C

16-Bit Information Option Register 2

Room temperature ADC reading of Temperature Sensor; value

set during factory test

Table 4-27 FlexCAN Registers Address Map

(FC_BASE = $00 F800)

FlexCAN is NOT available in the 56F8122 device

Register Acronym

Address Offset

Register Description

FCMCR

$0

Module Configuration Register

Reserved

FCCTL0

$3

Control Register 0 Register

FCCTL1

$4

Control Register 1 Register

FCTMR

$5

Free-Running Timer Register

FCMAXMB

$6

Maximum Message Buffer

Configuration Register

Reserved

FCRXGMASK_H

$8

Receive Global Mask High Register

FCRXGMASK_L

$9

Receive Global Mask Low Register