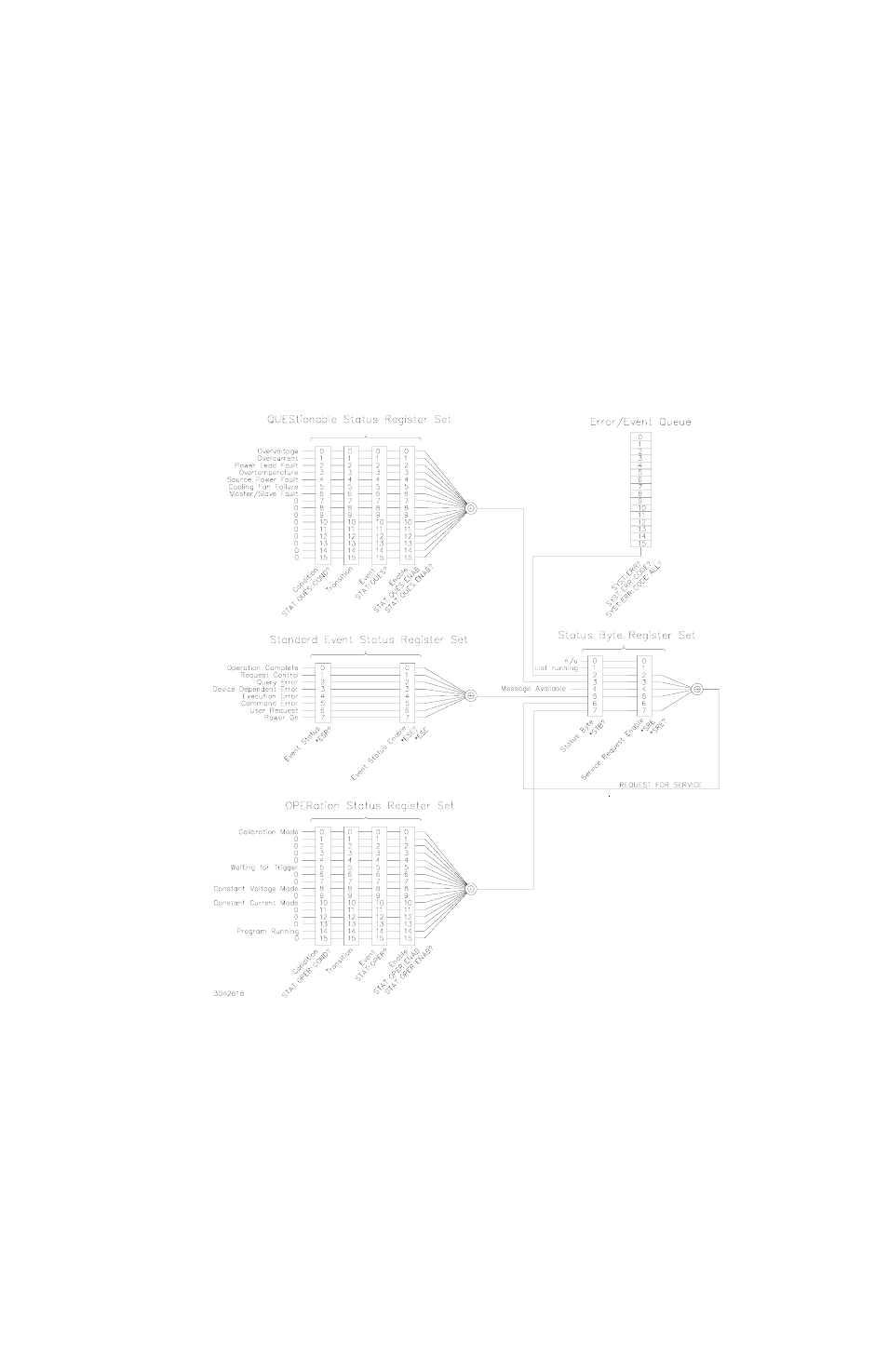

Figure 1-2. status reporting structure, Status reporting structure -5 – KEPCO KLP Series Developers Guide, Rev 3 User Manual

Page 15

KLP-DEV 041213

1-5

For example, if an overvoltage error is detected, bit 0 of the Questionable Status Condition reg-

ister is set. The 0 to 1 transition causes bit 0 to be stored as a 1 in the corresponding Event reg-

ister. If bit 0 of the Questionable Status Enable register has bit 0 set, bit 3 of the Status Byte

(STB) register is asserted. If bit 3 of the Service Request Enable (SRE) register is also set to 1,

then bit 6 of the STB is set to 1 (true), causing the power supply to assert the SRQ line to the

host computer.

FIGURE 1-2. STATUS REPORTING STRUCTURE

See also other documents in the category KEPCO Power suppliers:

- ABC-DM SERIES (96 pages)

- ATE (all models) QUICK START GUIDE (8 pages)

- SN 488-D (94 pages)

- SN 488-D (14 pages)

- SN 488-D (16 pages)

- BHK-MG 200W (Full Rack) Series (152 pages)

- BHK-MG 40W (Half Rack) Series (148 pages)

- BIT 232 (72 pages)

- BIT 4882 (56 pages)

- BIT 4886 Quick Start Guide (4 pages)

- BIT 4886 Operator Manual (92 pages)

- BOP 100W, 200W, 400W (M, D) Quick Start Guide (8 pages)

- BOP 20-5ML Modification Sheet (1 page)

- BOP 20-10MC Modification Sheet (2 pages)

- BOP 36-6MC Modification Sheet (2 pages)

- BOP 100-2MC Modification Sheet (2 pages)

- BOP 50-4MC Modification Sheet (2 pages)

- BOP 100-2ML Modification Sheet (2 pages)

- BOP 72-3ML Modification Sheet (2 pages)

- BOP 50-4ML Modification Sheet (2 pages)

- BOP 36-6ML Modification Sheet (2 pages)

- BOP 20-10ML Modification Sheet (2 pages)

- BOP 72-6MC Modification Sheet (2 pages)

- BOP 36-12MC Modification Sheet (2 pages)

- BOP 20-20MC Modification Sheet (2 pages)

- BOP 100-4ML Modification Sheet (2 pages)

- BOP 72-6ML Modification Sheet (2 pages)

- BOP 50-8ML Modification Sheet (2 pages)

- BOP 36-12ML Modification Sheet (2 pages)

- BOP 20-20ML Modification Sheet (2 pages)

- BOP 1KW-MG Quick Start Guide (16 pages)

- BOP 1KW-MG Quick Reference Guide (2 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.4.12 and higher (196 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.4.08 to 4.11 (194 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.3.05 to 4.07 (194 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.2.48 to 3.04 (188 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.2.38 to 2.47 (188 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.2.01 to 2.37 (176 pages)

- BOP 1KW as Solar Device Tester Quick Start Guide (3 pages)

- BOP-GL 1KW Quick Start Guide (16 pages)

- BOP-GL 1KW Operator Manual Firmware Ver.3.05 and higher (168 pages)

- BOP-HV (48 pages)

- CA 26 (2 pages)

- CA 27 (2 pages)

- CA 29 (2 pages)