Figure b-6. using status commands and queries, B.63 status:questionable[:event]? query, B.63 – KEPCO KLP Series Developers Guide, Rev 3 User Manual

Page 123: Stat, S b.63, Stat:ques

KLP 041213

B-17

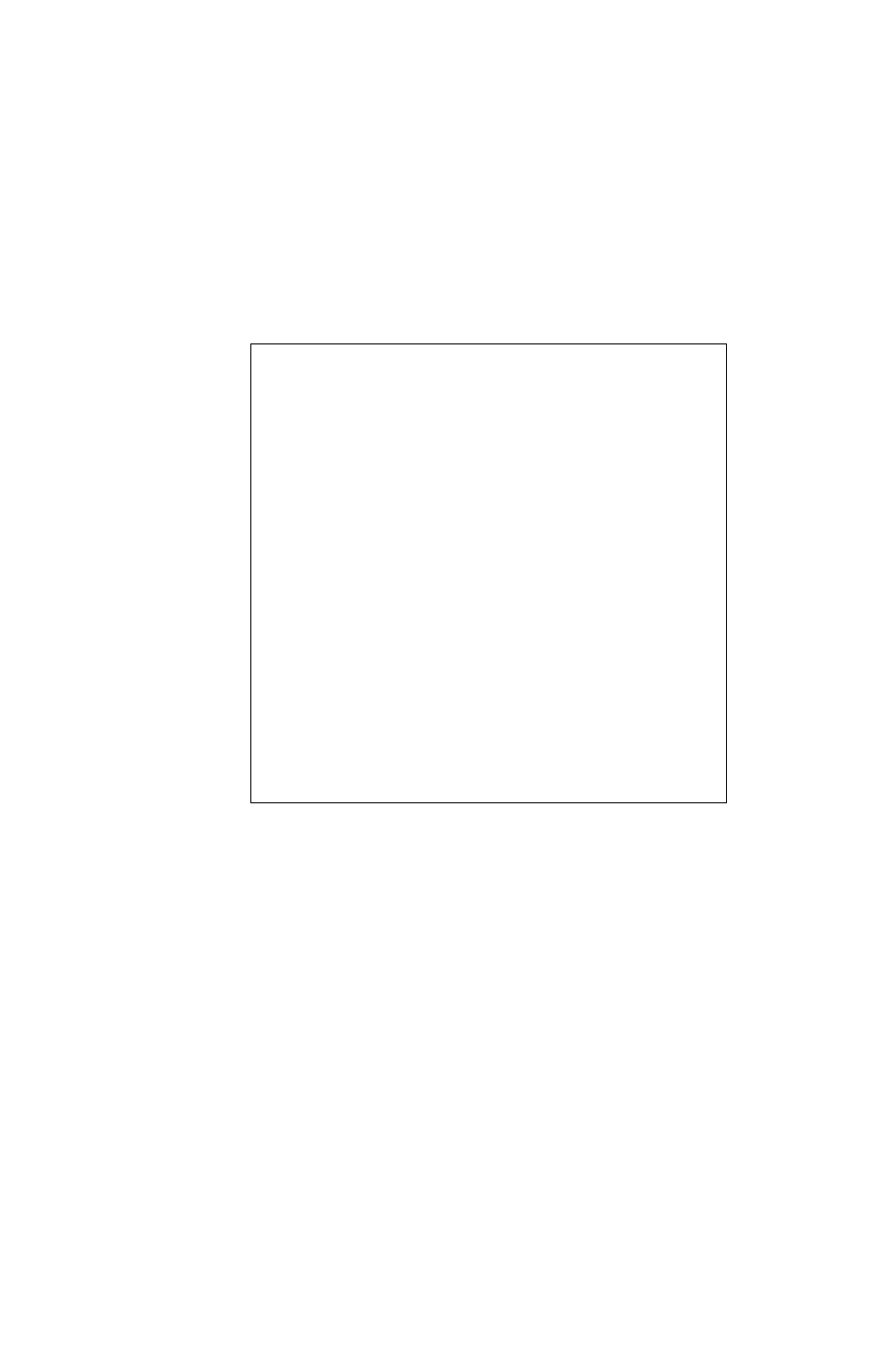

FIGURE B-6. USING STATUS COMMANDS AND QUERIES

B.63 STATus:QUEStionable[:EVENt]? QUERY

STAT:QUES?

Syntax:

Short Form: STAT:QUES[EVEN]?

Long Form: STATus:QUEStionable[EVENT]?

Return Value:

Description: Indicates questionable events that occurred since previous STAT:QUES? query. Returns the

value of the Questionable Event register (see Table B-3). The Questionable Event register is a

read-only register which holds (latches) all events. Reading the Questionable Event register clears it.

(See example, Figure B-6.)

NOTE: Removing source power from the unit (e.g., setting POWER ON/OFF circuit breaker to OFF)

causes the unit to generate and store the PWR bit. Therefore the first query of the Questionable Event

Register after the unit is turned on will always show a PWR fault - this is normal.

NOTE: The following example assumes KLP 75-33-1200 with virtual model set for 75V, 16A and

output operating in voltage stabilization mode. See Figure B-3 for directions on program-

ming virtual model limits.

OUTP ON

Power supply output is on.

VOLT 20;CURR 1

Power supply output is programmed to 20V, 1A.

SYST:ERR?

Returns 0, “No error” message.

STAT:OPER?

Returns 1280, indicating that power supply has entered both CV

and CC modes during start-up.

INIT:CONT ON

Continuous triggers enabled.

STAT:OPER:COND?

Power supply returns 288 (256 + 32), indicating power supply is in

constant voltage mode and Wait For Trigger is set.

STAT:OPER?

Returns 32, CV mode bit cleared by prior query, but continuous

triggering results in WTG bit always being set.

STAT:OPER:ENAB 1312

Mask enabled for CV, CC, and WTG bits.

STAT:OPER:ENAB?

Returns 1312 (1024 + 256 + 32), indicating CV, CC, and WTG bits

are set.

VOLT 30

Output voltage programmed to 30V; current remains at 1A.

*STB?

Return 128, Operation Status Summary bit is set.

STAT:QUES?

Returns 16, loss of source power detected. (This event was set at

prior power-down of power supply and is retained for retrieval at

next power-up; reading the event register clears the bit.)

STAT:QUES:ENAB 3

Mask enabled for OVP and OCP bits (1 + 2).

STAT:QUES:ENAB?

Returns 3 (1 + 2) indicating OVP and OCP bits are enabled.

VOLT:PROT 25

Overvoltage protection limit set to 25V with output programmed to

30V, creating an OVP fault condition.

*STB?

Returns 136, Operation and Questionable Status bits were sets.

STAT:QUES?

Returns 1, overvoltage protection error detected.

STAT:QUES?

Returns 0, Reading prior register cleared register contents.

STAT:QUES:COND?

Returns 1, power supply is in overvoltage protection.

OUTP?

Returns 0, output set to off when overvoltage error detected.

STAT:PRES

Operation enable and Questionable enable registers reset.

STAT:QUES:ENAB?

Returns 0, Questionable Condition Enable register reset prevents

any questionable events from being reported.

STAT:OPER:ENAB?

Returns 0, Operation Condition Enable register reset prevents

any operational events form being reported.