Dac chcd register 0 0x40 – Sundance SMT943 User Manual

Page 41

User Manual SMT943

Page 41 of 54

Last Edited: 23/08/2011 17:24:00

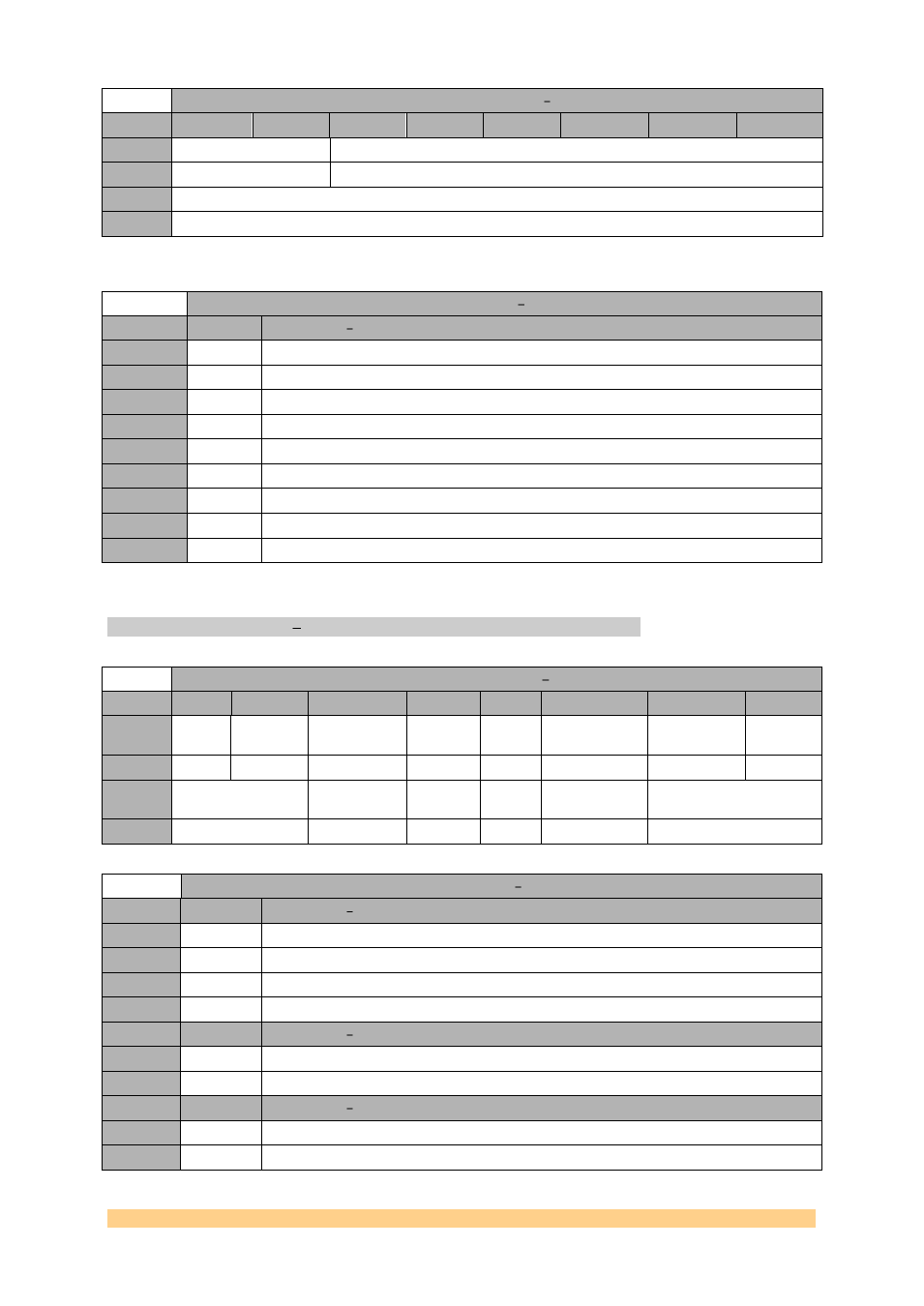

ADC Chab Register 9 0x39

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Offset Pedestal ChB (Common)

Default

‘00’

1

Reserved

Default

‘00000000’

ADC Chab Register 9 0x39

Setting

Bit 5:0

Description Offset Pedestal ChA (Common)

0

‘011111’

Pedestal=+31LSBs

1

‘011110’

Pedestal=+30LSBs

2

…

…

3

‘000000’

Pedestal=0

4

…

…

5

‘111111’

Pedestal=-1LSB

6

‘111110’

Pedestal=-2LSB

7

…

…

8

‘100000’

-32LSBs

DAC chcd Register 0 0x40.

DAC chcd Register 0 0x40

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserv

ed

Clk1_in_e

na

Clk1c_in_ena

Reserved Fir4_en qmc_offset_en

a

qmc_corr_en

a

mixer_en

a

Default

‘1’

‘1’

‘1’

‘0’

‘0’

‘0’

‘0’

‘0’

0

insel_mode

Reserved

Synchr_c

lkin

Twos

inv_clk

interp_value

Default

‘00’

‘0’

‘0’

‘0’

‘0’

‘00’

DAC chcd Register 0 0x40

Setting

Bit 1:0

Description interpolation value

0

00

1x.

1

01

2x.

2

10

4x.

3

11

8x.

Setting

Bit 2

Description inv_clk

0

0

Input clock not inverted.

1

1

Input clock inverted.

Setting

Bit 2

Description twos

0

0

Binary format

1

1

Two’s complement format.