Adc chab register 0 0x30, Adc chab register 1 0x31 – Sundance SMT943 User Manual

Page 35

User Manual SMT943

Page 35 of 54

Last Edited: 23/08/2011 17:24:00

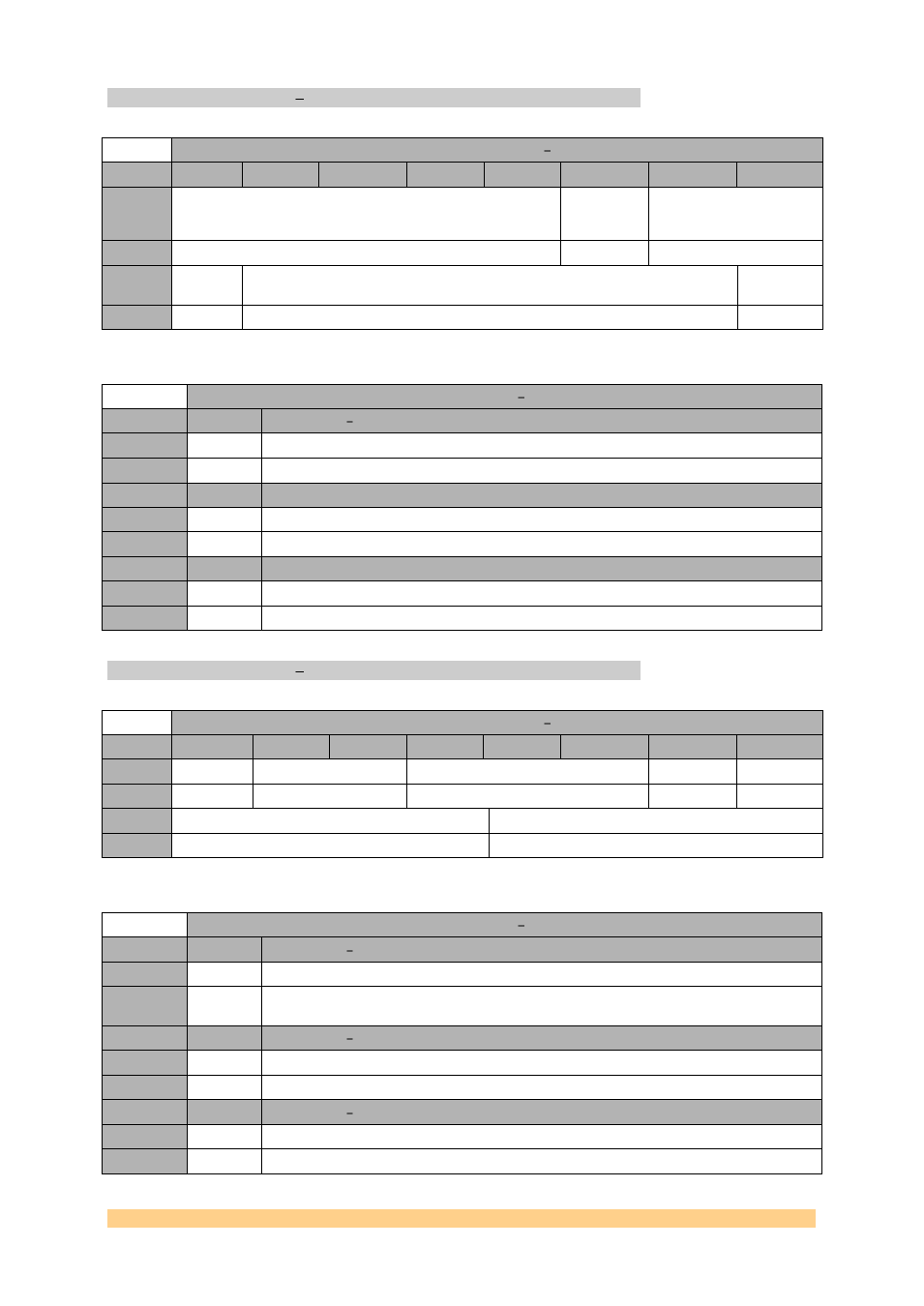

ADC Chab Register 0 0x30.

ADC Chab Register 0 0x30

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserved

Enable Low

Speed

Mode

Reserved

Default

‘00000’

‘0’

‘00’

0

Software

Reset

Reserved

SerialRead

Out

Default

‘0’

‘000000’

‘0’

ADC Chab Register 0 0x30

Setting

Bit 0

Description SerialReadOut

0

‘0’

Serial readout disabled.

1

‘1’

Serial readout enabled.

Setting

Bit 7

Description - Software Reset

0

‘0’

Normal mode of operation.

1

‘1’

Resets all internal registers and self-clears to ‘0’.

Setting

Bit 10

Description - Enable Low Speed Mode

0

‘0’

Low Speed Mode disabled. Sampling rates >100MSPS.

0

‘1’

Low Speed Mode enabled. Sampling rates <=100 MSPS.

ADC Chab Register 1 0x31.

ADC Chab Register 1 0x31

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Reference

Reserved

Standby

Reserved

Default

’0’

‘00’

‘000’

‘0’

‘0’

1

Reserved

PowerDownModes

Default

‘0000’

‘0000’

ADC Chab Register 1 0x31

Setting

Bit 1

Description Standby.

0

‘0’

Normal mode of operation.

1

‘1’

Both ADC channels are put into standby mode (internal ref and output buffers still

active).

Setting

Bit 6:5

Description Reference.

0

‘01’

Internal Reference enabled.

1

‘11’

External Reference enabled.

Setting

Bit 11:8

Description Power down modes.

0

‘0000’

Pins ctrl1, 2 and 3 determine power down modes.

1

‘1000’

Normal mode of operation.