Sundance SMT943 User Manual

Page 30

User Manual SMT943

Page 30 of 54

Last Edited: 23/08/2011 17:24:00

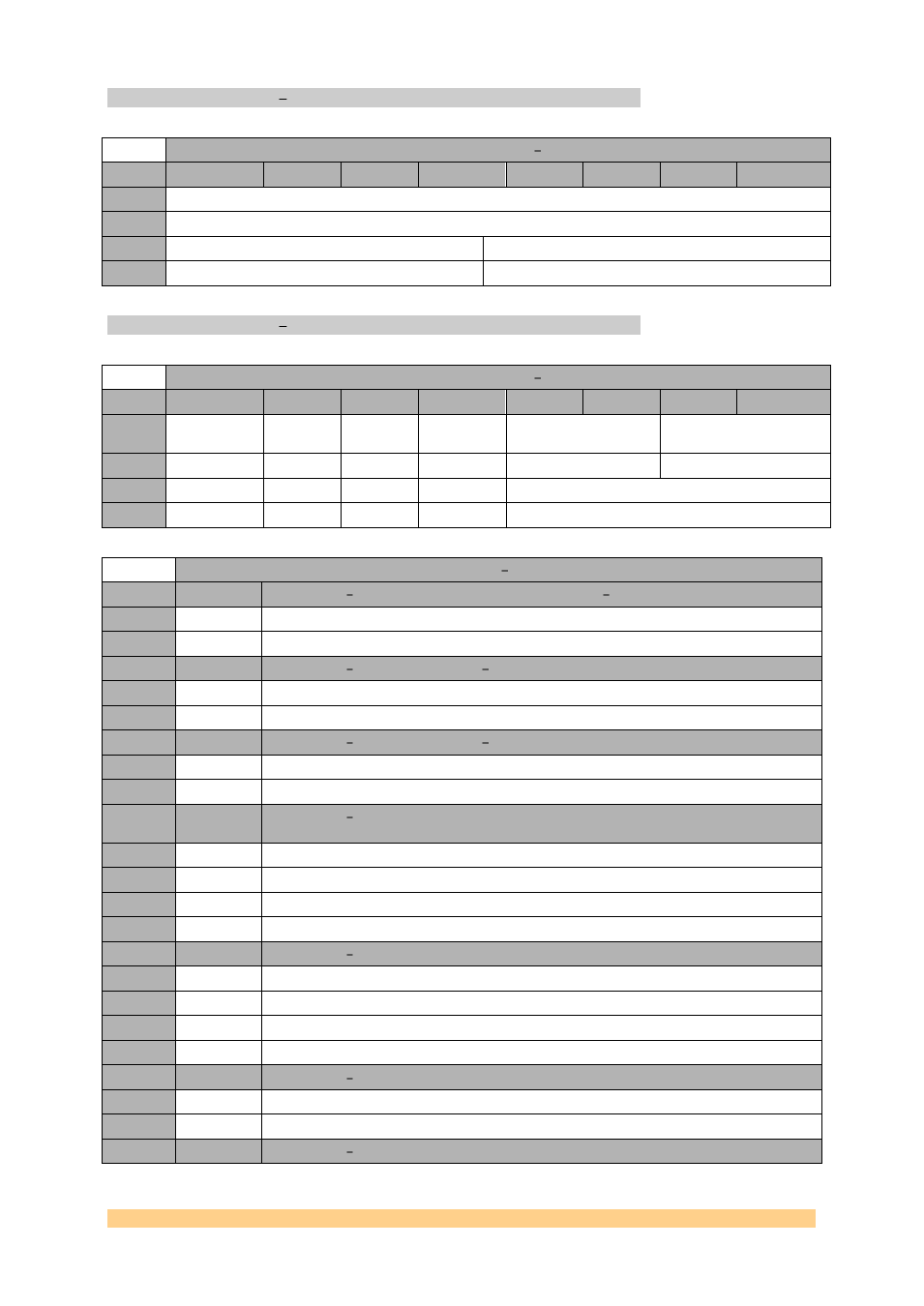

CLOCK Register 11 0x21.

Clock Register 11 0x21

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserved

Default

‘01101000’

0

Reserved

Reserved

Default

‘0000’

‘0000’

CLOCK Register 12 0x22.

Clock Register 12 0x22

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

INDET_BP

START_B

YPASS

DIVSYNC

_DIS

Reserved

LOCKW

HOLD_CNT

Default

‘0’

‘0’

‘0’

‘0’

‘00’

‘00’

0

Reserved

HOLD

Reserved

HOLDF

Reserved

Default

‘0’

‘0’

‘0’

‘0’

‘1001’

Reset Register 12 0x22

Setting

Bit 4

Description Frequency Hold Over (External) enable HOLDF

0

‘0’

Off

1

‘1’

On

Setting

Bit 6

Description equals to HOLD pin HOLD

0

‘0’

Tri-state charge pump

1

‘1’

Setting

Bit 6

Description equals to HOLD pin HOLD

0

‘0’

Tri-state charge pump

1

‘1’

Setting

Bit 9:8

Description Hold function reactivates after a number of reference clock cycles -

HOLD_CNT

0

‘00’

64 clock cycles

1

‘01’

128 clock cycles

2

‘10’

256 clock cycles

3

‘11’

512 clock cycles

Setting

Bit 11:10

Description Extended lock detect window - LOCKW

0

‘00’

1

‘01’

2

‘10’

3

‘11’

Setting

Bit 13

Description DIVSYNC_DIS

0

‘0’

Start signal is synchronised to N/M divider input clock

1

‘1’

Setting

Bit 14

Description START_BYPASS