Adc chab register 7 0x37 – Sundance SMT943 User Manual

Page 39

User Manual SMT943

Page 39 of 54

Last Edited: 23/08/2011 17:24:00

Setting

Bit 2:0

Description Test Patterns ChA

0

‘000’

Normal Mode of Operation

1

‘001’

Outputs all zeroes

2

‘010’

Outputs all ones

3

‘011’

Outputs toggle pattern (0x1555 and 0x2AAA)

4

‘100’

Outputs digital ramp (0->16383)

5

‘101’

Outputs custom pattern

Setting

Bit 13:8

Description Offset Pedestal ChA (Common)

0

‘011111’

Pedestal=+31LSBs

1

‘011110’

Pedestal=+30LSBs

2

…

…

3

‘000000’

Pedestal=0

4

…

…

5

‘111111’

Pedestal=-1LSB

6

‘111110’

Pedestal=-2LSB

7

…

…

8

‘100000’

-32LSBs

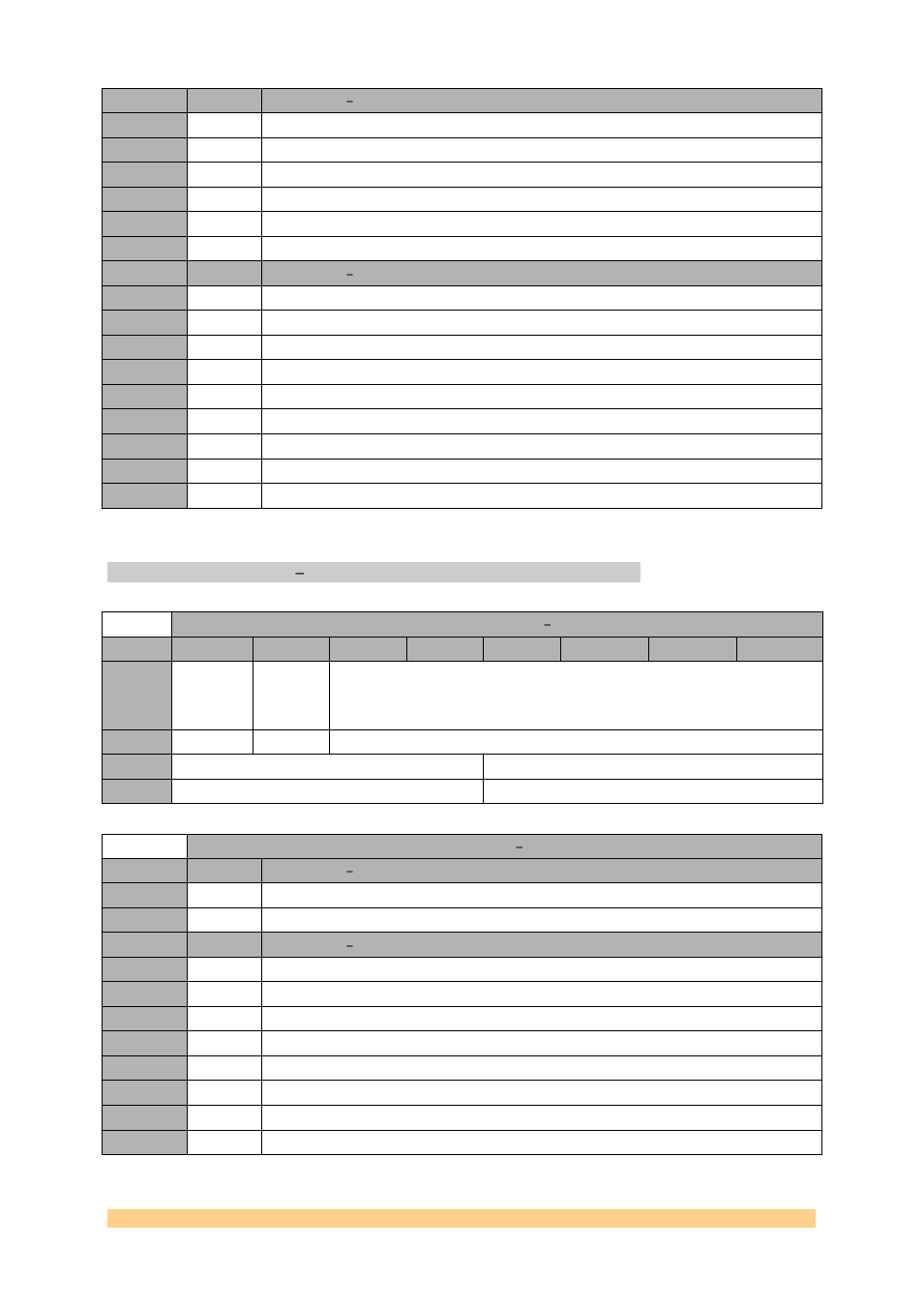

ADC Chab Register 7 0x37.

ADC Chab Register 7 0x37

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Offset

Correctio

n Enable

ChB

Reserved

Default

‘0’

‘0’

‘000000’

1

Gain ChB (Common)

Offset Correction Time Constant ChB

Default

‘0000’

‘0000’

ADC Chab Register 7 0x37

Setting

Bit 6

Description Offset Correction Enable ChB.

0

‘0’

Offset Correction Disabled.

1

‘1’

Offset Correction Enabled.

Setting

Bit 11:8

Description Offset Correction Time Constant (number of clock cycles) ChB

0

‘0000’

256k

1

‘0001’

512k

2

‘0010’

1Meg

3

‘0011’

2Meg

4

‘0100’

4Meg

5

‘0101’

8Meg

6

‘0110’

16Meg

7

‘0111’

32Meg