Clock register 3 0x13, Clock register 4 0x14 – Sundance SMT943 User Manual

Page 23

User Manual SMT943

Page 23 of 54

Last Edited: 23/08/2011 17:24:00

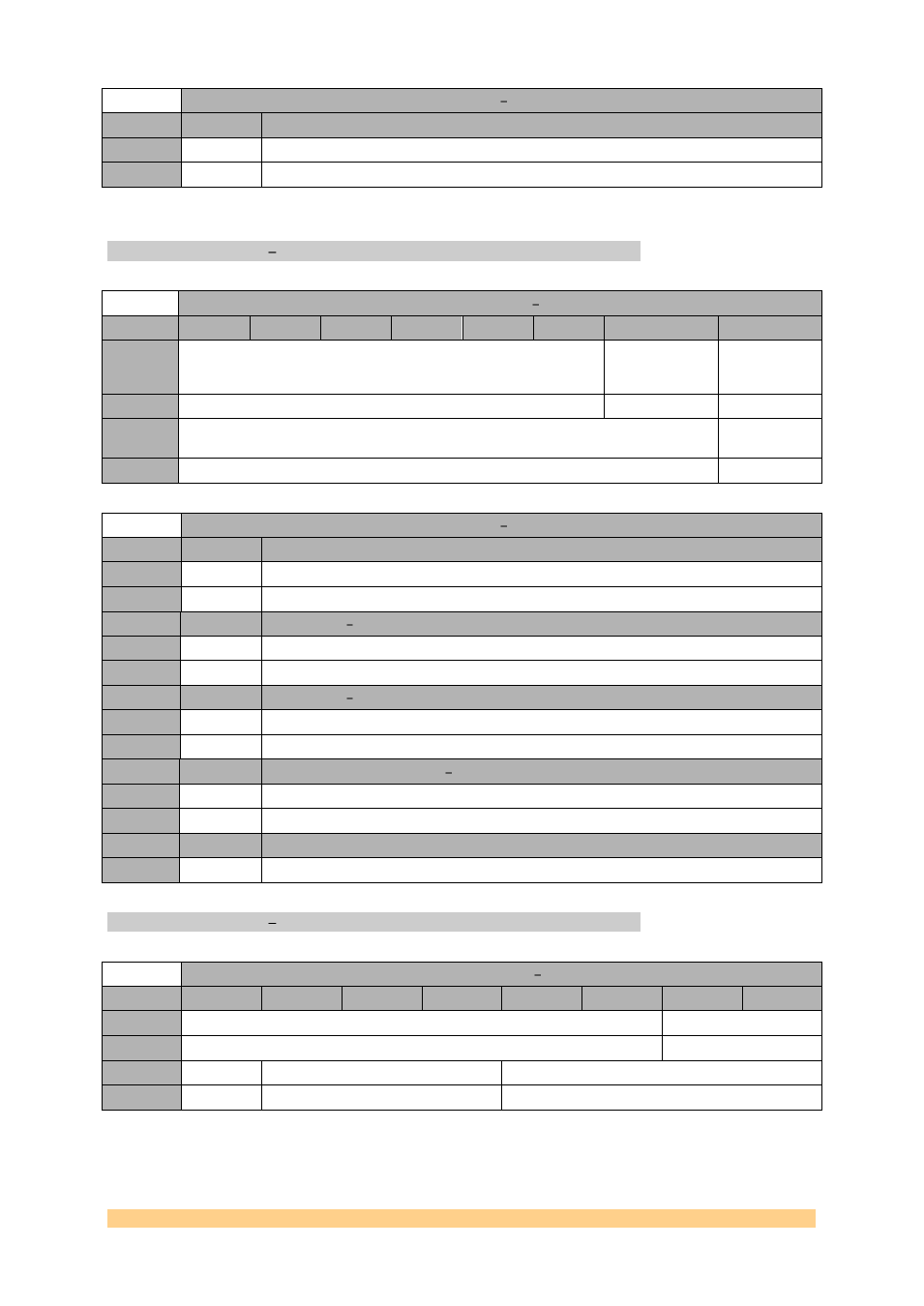

Reset Register 2 0x12

Setting

Bit 15:10

Description Coarse Phase Adjustment[5:0] DAC chc&d clk1 and clk2

0

0

1

1

CLOCK Register 3 0x13.

Clock Register 3 0x13

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Output0 (DAC chc&d clk2) Mode

PECL1HISWING

Output

Divider

Enable

Default

‘100000’

‘0’

‘0’

0

Output Divider Ratio DAC chc&d clk1 and clk2

Coarse Phase

Adjustment[6]

Default

‘0000000’

‘0’

Reset Register 3 0x13

Setting

Bit 0

Description - Coarse Phase Adjustment[6] DAC chc&d clk1 and clk2

0

0

1

1

Setting

Bit 7:1

Description Output Divider Ratio DAC chc&d clk1 and clk2

0

0

1

1

Setting

Bit 8

Description Output Divider Enable DAC chc&d clk1 and clk2

0

0

Divider disabled.

1

1

Divider enabled.

Setting

Bit 9

Description PECL1HISWING PECL output voltage swing (DAC chc&d clk2)

0

0

Normal Operation.

1

1

High PECL output voltage.

Setting

Bit 15:10

Description Output1 (DAC chc&d clk2) mode

0

0

LVPECL only: ‘100000’.

CLOCK Register 4 0x14.

Clock Register 4 0x14

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Coarse Phase Adjustment[5:0] (Output DAC cha&b clk1)

Delay N[2:1]

Default

‘000000’

‘00’

0

Delay N[0]

Delay M

Reserved

Default

‘0’

‘0’

‘0010’