Adc chab register 4 0x34, Adc chab register 5 0x35 – Sundance SMT943 User Manual

Page 37

User Manual SMT943

Page 37 of 54

Last Edited: 23/08/2011 17:24:00

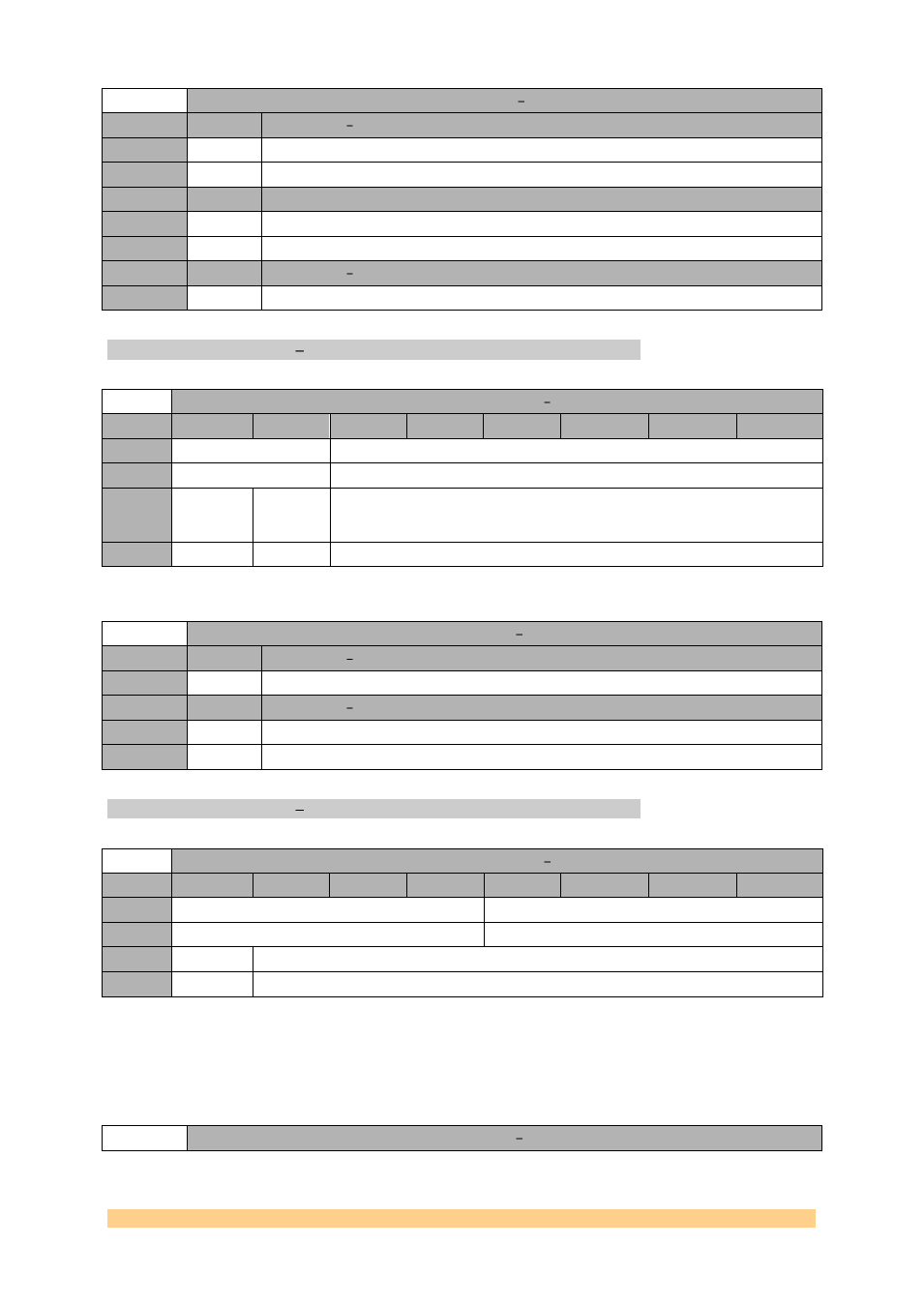

ADC Chab Register 3 0x33

Setting

Bit 2:1

Description Data Format

0

‘10’

2’s complement.

1

‘11’

Binary.

Setting

Bit 6

Description - Channel Control

0

‘0’

Common Control.

1

‘1’

Independent Control (Test pattern, Offset correction and SNR boost).

Setting

Bit 15:8

Description Custom Pattern (lsb)

0

ADC Chab Register 4 0x34.

ADC Chab Register 4 0x34

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Custom Pattern (msb)

Default

‘00’

‘000000’

1

Reserved

Offset

Correctio

n Enable

Reserved

Default

‘0’

‘0’

‘000000’

ADC Chab Register 4 0x34

Setting

Bit 5:0

Description Custom Pattern (msb).

0

Setting

Bit 14

Description Offset Correction Enable ChA.

0

‘0’

Offset Correction Disabled.

1

‘1’

Offset Correction Enabled.

ADC Chab Register 5 0x35.

ADC Chab Register 5 0x35

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Gain ChA (Common)

Offset Correction Time Constant ChA

Default

‘0000’

‘0000’

1

Reserved

Fine Gain Adjustment ChA (Common)

Default

‘0’

‘0000000’

ADC Chab Register 5 0x35