Sundance SMT943 User Manual

Page 19

User Manual SMT943

Page 19 of 54

Last Edited: 23/08/2011 17:24:00

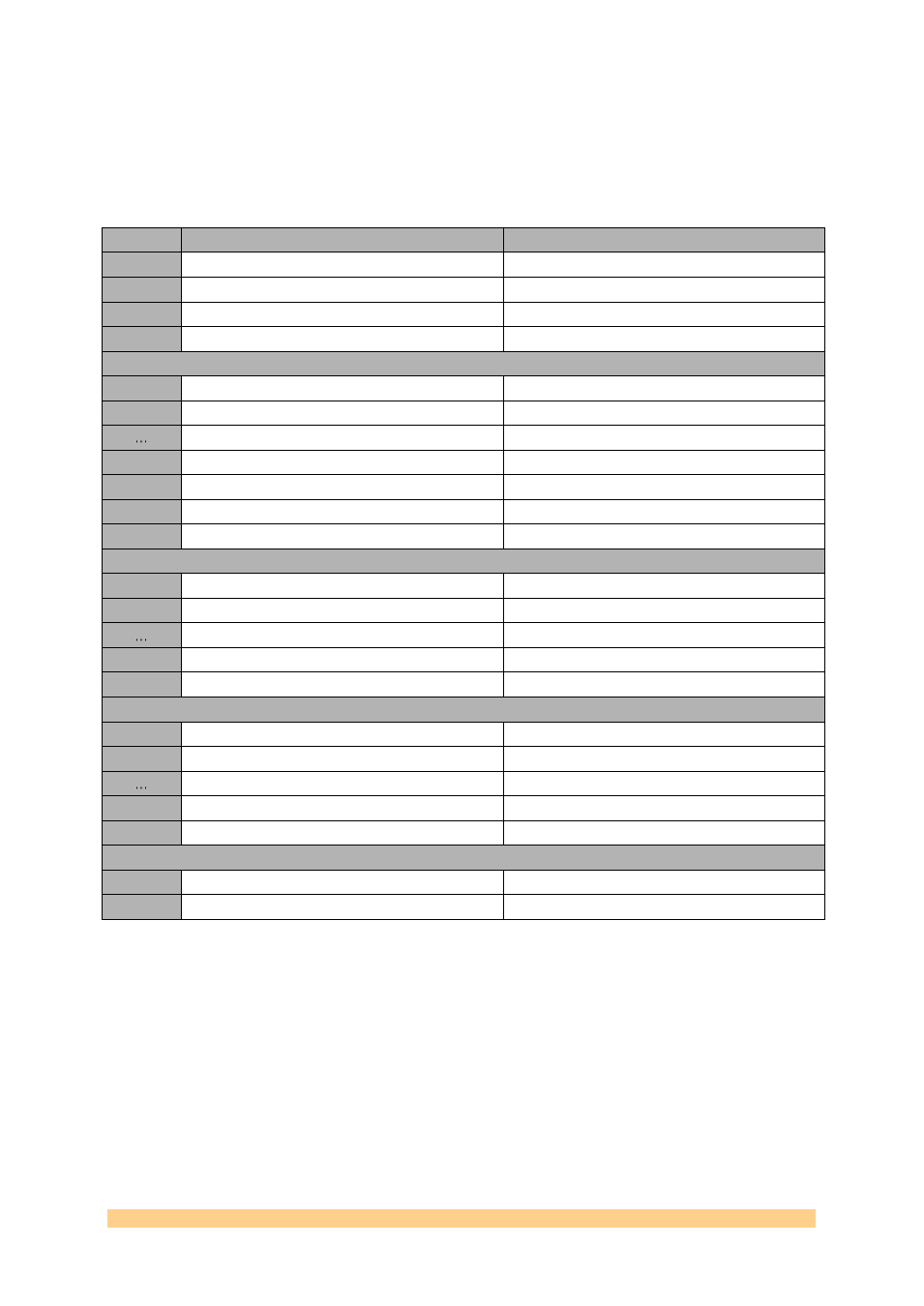

3.3.1.3 Memory Map

The write packets must contain the address where the data must be written to and

the read packets must contain the address where the required data must be read.

The following figure shows the memory map for the writable and readable Control

Registers on the SMT943:

Address

Writable Registers

Readable Registers

0x00

Reserved.

Reserved.

0x01

Board Control Register.

Firmware Version.

0x02

Reserved.

Clock Readback Register.

0x03

Reserved.

Board Status Register

Clock Section

0x10

Clock Register 0x0.

Read-back (FPGA Register) Clock Register 0x0.

0x11

Clock Register 0x1.

Read-back (FPGA Register) Clock Register 0x1.

…

…

0x28

Clock Register 0x18.

Read-back (FPGA Register) Clock Register 0x18.

0x29

Clock Register 0x19.

Read-back (FPGA Register) Clock Register 0x19.

0x2A

Clock Readback Address Register (LSB)

0x2B

Clock Readback Address Register (MSB)

ADCab Section

0x30

ADCab Register 0x0.

Read-back (FPGA Register) ADCab Register 0x0.

0x31

ADCab Register 0x1.

Read-back (FPGA Register) ADCab Register 0x1.

…

...

0x3D

ADCab Register 0x8.

Read-back (FPGA Register) ADCab Register 0x8.

0x3E

ADCab Register 0x9.

Read-back (FPGA Register) ADCab Register 0x9.

DACcd Section

0x40

DACcd Register 0x0.

Read-back (FPGA Register) DACcd Register 0x0.

0x41

DACcd Register 0x1.

Read-back (FPGA Register) DACcd Register 0x1.

…

...

0x4D

DACcd Register 0xD.

Read-back (FPGA Register) DACcd Register 0xD.

0x4E

DACcd Register 0xE.

Read-back (FPGA Register) DACcd Register 0xE.

DACcd DCM Section

0x50

DCM DAC chc&d Phase shift.

Reserved

Figure 17

– Register Memory Map.