Altera Arria V GX FPGA Development Board User Manual

Page 86

2–76

Chapter 2: Board Components

Power Supply

Arria V GX FPGA Development Board

November 2013

Altera Corporation

Reference Manual

3

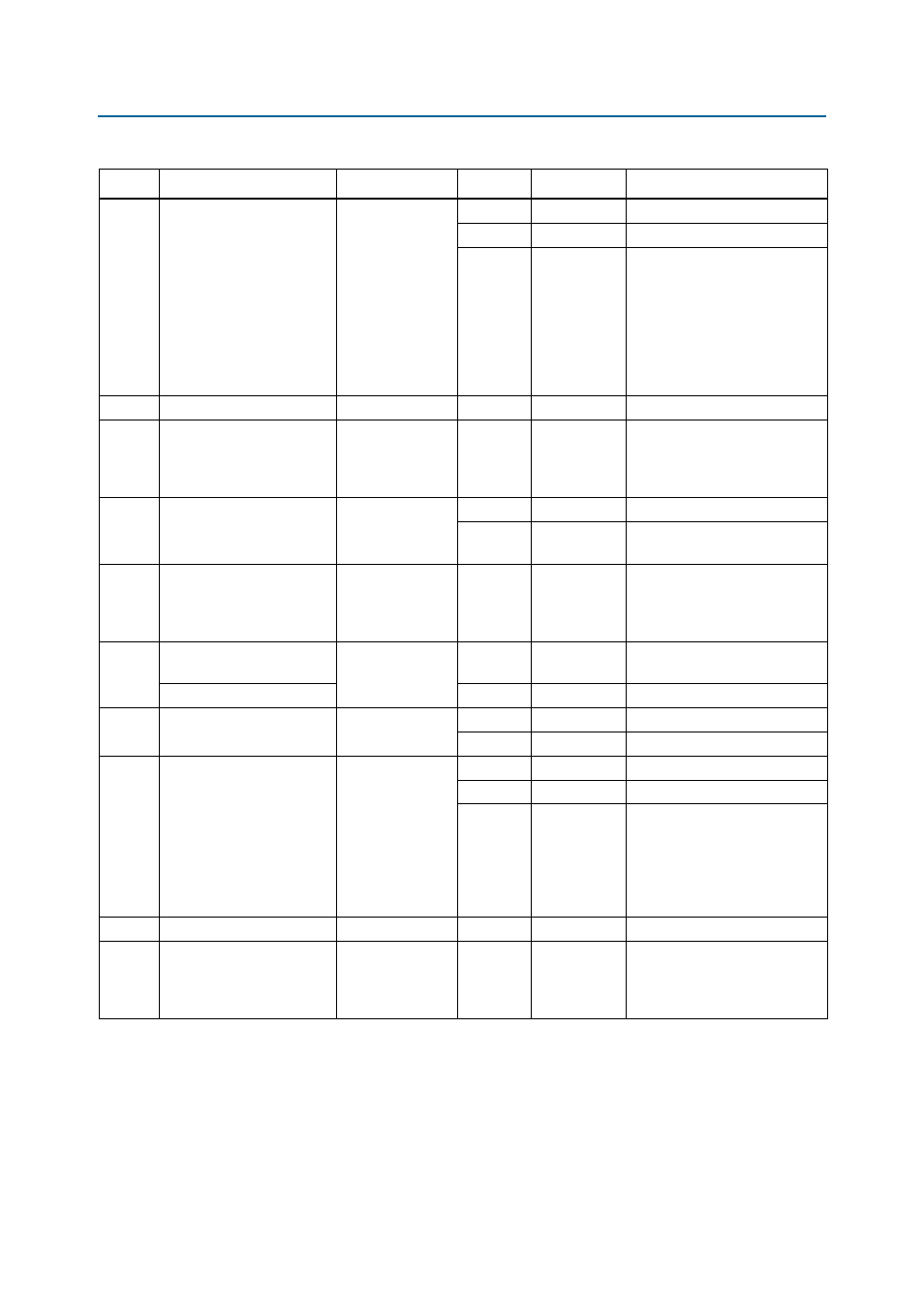

A5A_VCCPD_PGM_IO_2.5V A5A_VCCPD/PGM

2.5 V

VCCPD

I/O pre-drivers

2.5 V

VCCPGM

Configuration I/O

2.5 V

VCCIO_4A,

VCCIO_4B,

VCCIO_4C,

VCCIO_4D,

VCCIO_7A,

VCCIO_7B,

VCCIO_7C,

VCCIO_7D

VCC I/O banks 4 and 7

4

A5A_VCCINT

A5A_VCCINT

1.1 V

VCC, VCCP

FPGA core and periphery power

5

A5A_VCCIO_1.5V

A5A_VCCIO_1.5V

1.5 V

VCCIO_8A,

VCCIO_8B,

VCCIO_8C,

VCCIO_8D

VCCIO bank 8 (DDR3A)

6

A5A_VCCD_PLL_1.5V

A5A_VCCD_PLL

1.5 V

VCCD_FPLL

PLL digital power

1.5 V

VCCH_GXB

XCVR block level transmit

buffers

7

A5A_VCCIO_1.8V

A5A_VCCIO_1.8V

1.8 V

VCCIO_3A,

VCCIO_3B,

VCCIO_3C,

VCCIO_3D

VCC I/O bank 3 (QDRII+)

8

A5B_VCCR_VCCL_GXB

A5B_XCVR_GXB

1.1 V

VCCR_GXB,

VCCL_GXB

XCVR analog receive and clock

network

A5B_VCCT_GXB

1.1 V

VCCT_GXB

XCVR transmitter power

9

A5B_VCCA_2.5V

A5B_VCCA

2.5 V

VCCA_FPLL

PLL analog power

2.5 V

VCC_AUX

Auxiliary

10

A5B_VCCPD_PGM_IO_2.5V A5B_VCCPD/PGM

2.5 V

VCCPD

I/O pre-drivers

2.5 V

VCCPGM

Configuration I/O

2.5 V

VCCIO_3A,

VCCIO_3B,

VCCIO_7A,

VCCIO_7B,

VCCIO_7C,

VCCIO_7D

VCC I/O banks 3A, 3B and 7

11

A5B_VCCINT

A5B_VCCINT

1.1 V

VCC

FPGA core and periphery power

12

A5B_VCCIO_1.5V

A5B_VCCIO_1.5V

1.5 V

VCCIO_8A,

VCCIO_8B,

VCCIO_8C,

VCCIO_8D

VCCIO bank 8 (DDR3A)

Table 2–62. Power Measurement Rails (Part 2 of 3)

Switch

Schematic Signal Name

GUI Name

Voltage

Device Pin

Description