Power distribution system, Power distribution system –42 – Altera Cyclone V E FPGA Development Board User Manual

Page 50

2–42

Chapter 2: Board Components

Power Supply

Cyclone V E FPGA Development Board

March 2013

Altera Corporation

Reference Manual

Power Distribution System

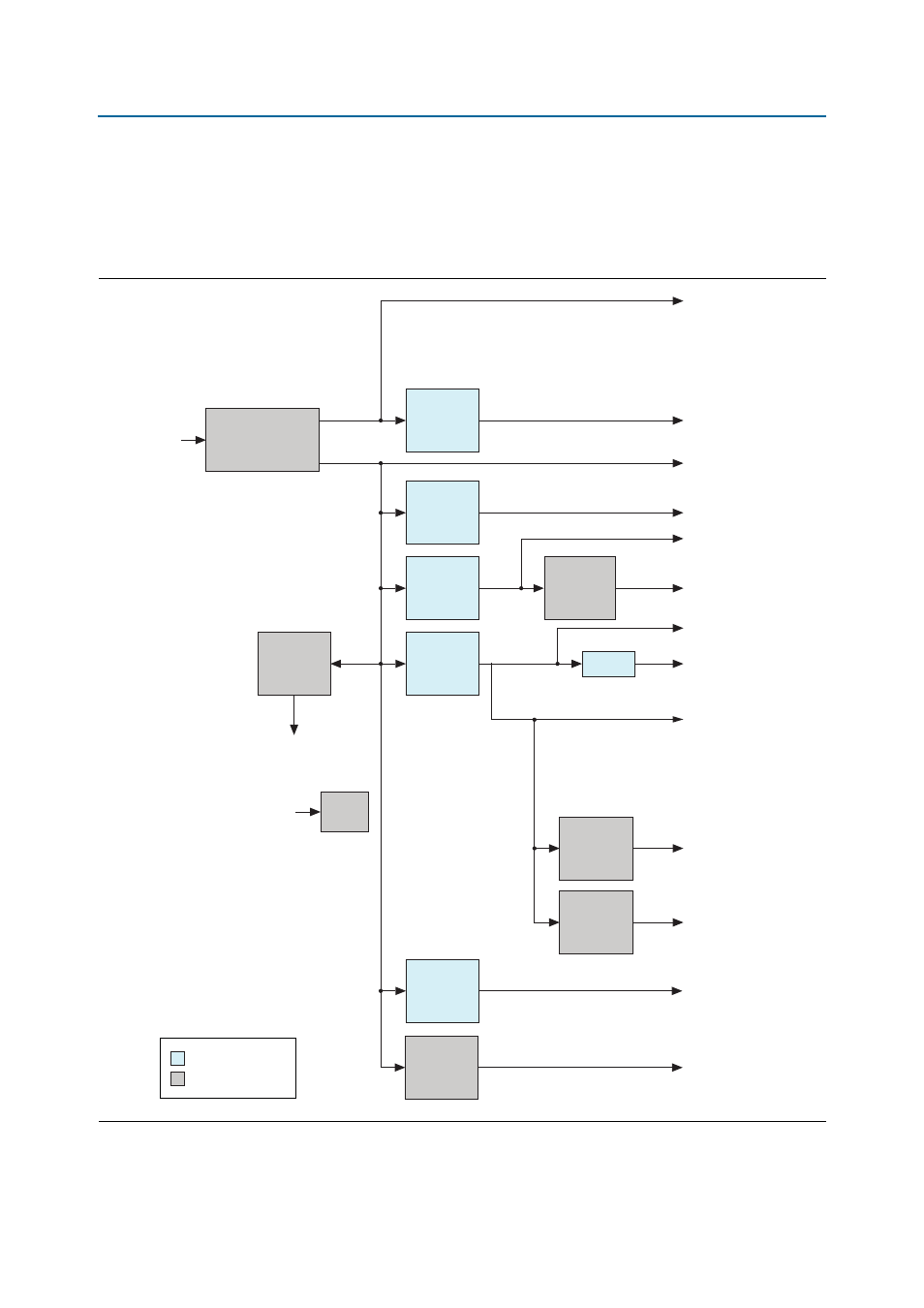

shows the power distribution system on the development board. Regulator

inefficiencies and sharing are reflected in the currents shown, which are conservative

absolute maximum levels.

Figure 2–9. Power Distribution System

1.2 V LDO

1.5 A, +/- 5%

LTC3026

HSMC, Fan

EEPROM

HSMC

MAX II VCCIO

MAX V VCCIO

USB-Blaster II PHY VCC

Clock Buffer

EPCQ

USB PHY

Battery

3 V

5.37 V LDO

20 mA, +/- 5%

LT3009

5.37 V at 0.3 mA

Power

Monitor

1.0 V LDO

1.5 A, +/- 5%

LTC3026

1.0 V at

500 mA

1.8 V LDO

500 mA, +/- 5%

LTC3025-1

1.8 V at

200 mA

Enet PHY

Flash

LPDDR2

MAX II VCCINT

MAX V VCCINT

Enet PHY

SSRAM

Flash

Max V VCCIO

MAX II VCCIO

Oscillators, Clock

Generators, and Buffers

USB PHY

RS-232

Filter

VCC Core

VCCIO

LPDDR2

3.3 V at 3.1 A

12 V at 4.25 A

DC Input

14 - 20 V

FPGA Power Rails

Board Main Power Rails

1.2 V at 650 mA

1.1 V Low Noise

Switcher

8A, +/- 30 mV

LTC3608

1.1 V at 4.1 A

1.5 V Switcher

1.5 A, +/- 5%

LTC3600

1.5 V at

1.2 A

2.5 V Switcher

8 A, +/- 5%

LTC3608

2.5 V at 3.2 A

3.3 V Switcher

300 mA, +/- 5%

LTC3103

2.5 V at 3 A

3.3 V at 200 mA

VCCIO

VCCPD

VCCPGM

LCD Level Shifter

0.75 VTT LDO

5V at 8.8 mA

12 V (7A) and 3.3 V (5A)

Switcher +/- 5%

LTC3855 Dual Switcher

5 V LDO

20 mA, +/- 5%

LT3009

FPGA

VCCBAT

VCCIO

VCCPD

VCCAUX

VCCA_FPLL

VCCBAT

0.75 V LDO

3 A, +/- 5%

TPS51100DGQ

0.75 V at

350 mA

DDR3 VTT

VCCIO

DDR3