Altera Cyclone V E FPGA Development Board User Manual

Page 33

Chapter 2: Board Components

2–25

Components and Interfaces

March 2013

Altera Corporation

Cyclone V E FPGA Development Board

Reference Manual

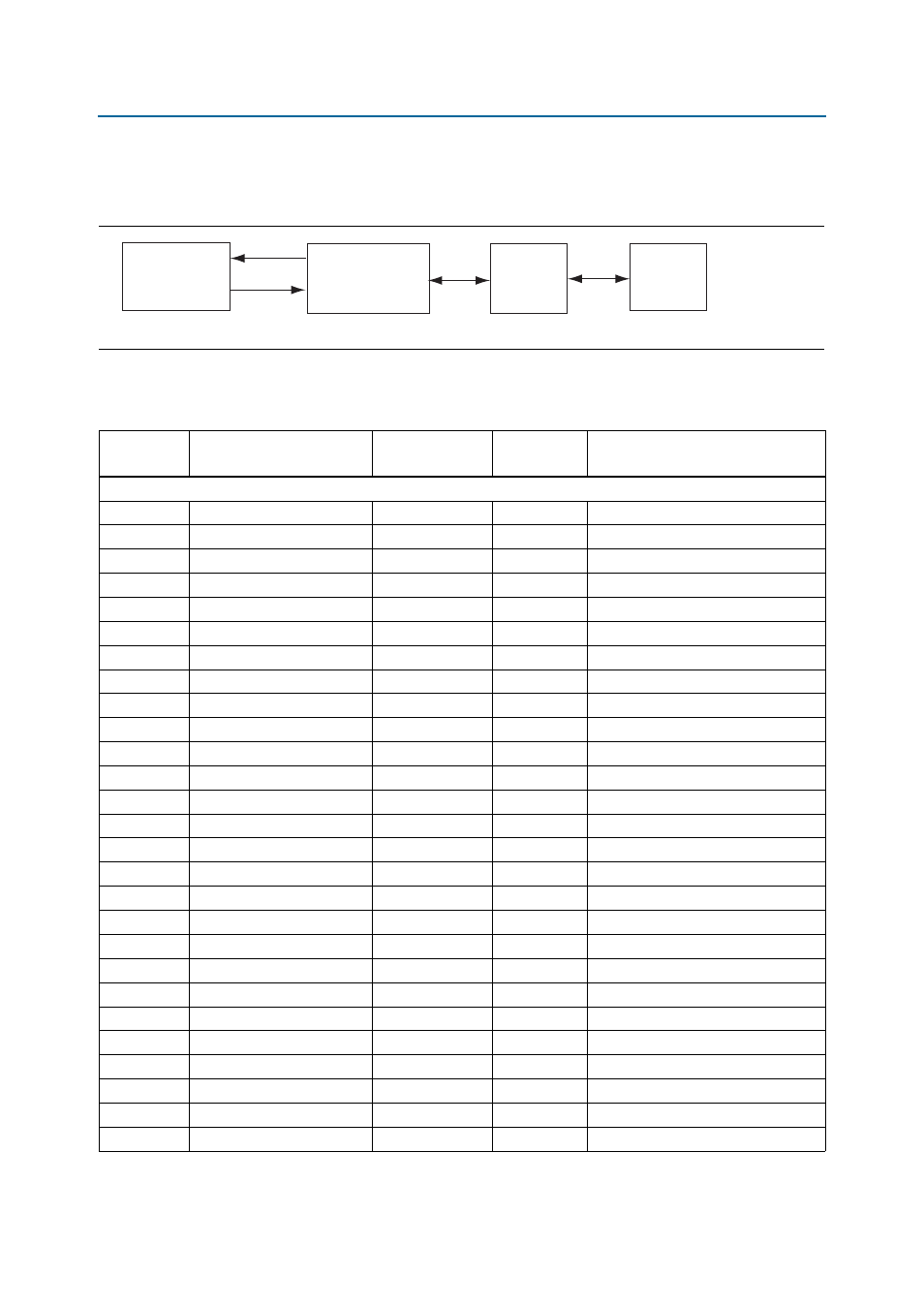

shows the RGMII interface between the FPGA (MAC) and Marvell 88E1111

PHY.

lists the Ethernet PHY interface pin assignments.

Figure 2–7. RGMII Interface between FPGA (MAC) and Marvell 88E1111 PHY

10/100/1000 Mbps

Ethernet MAC

Marvell 88E1111

PHY

Device

Transformer

RJ45

RGMII Interface

TXD[3:0]

RXD[3:0]

CAT 5 UTP:

- 10BASE-T

- 100BASE-TX

- 1000BASE-T

Table 2–20. Ethernet PHY Pin Assignments, Signal Names and Functions (Part 1 of 3)

Board

Reference

Schematic Signal Name

Cyclone V E FPGA

Pin Number

I/O Standard

Description

Ethernet PHY A (U14)

8

ENETA_GTX_CLK

H27

2.5-V CMOS

125-MHz RGMII transmit clock

23

ENETA_INTN

J27

2.5-V CMOS

Management bus interrupt

60

ENETA_LED_DUPLEX

—

2.5-V CMOS

Duplex or collision LED. Not used

70

ENETA_LED_DUPLEX

—

2.5-V CMOS

Duplex or collision LED. Not used

76

ENETA_LED_LINK10

—

2.5-V CMOS

10-Mb link LED

74

ENETA_LED_LINK100

—

2.5-V CMOS

100-Mb link LED

73

ENETA_LED_LINK1000

—

2.5-V CMOS

1000-Mb link LED

58

ENETA_LED_RX

—

2.5-V CMOS

RX data active LED

69

ENETA_LED_RX

—

2.5-V CMOS

RX data active LED

68

ENETA_LED_TX

—

2.5-V CMOS

TX data active LED

25

ENETA_MDC

G29

2.5-V CMOS

Management bus data clock

24

ENETA_MDIO

L25

2.5-V CMOS

Management bus data

28

ENETA_RESETN

N22

2.5-V CMOS

Device reset

2

ENETA_RX_CLK

T23

2.5-V CMOS

RGMII receive clock

95

ENETA_RX_D0

N26

2.5-V CMOS

RGMII receive data bus

92

ENETA_RX_D1

N27

2.5-V CMOS

RGMII receive data bus

93

ENETA_RX_D2

N24

2.5-V CMOS

RGMII receive data bus

91

ENETA_RX_D3

N25

2.5-V CMOS

RGMII receive data bus

94

ENETA_RX_DV

L25

2.5-V CMOS

RGMII receive data valid

11

ENETA_TX_D0

J28

2.5-V CMOS

RGMII transmit data bus

12

ENETA_TX_D1

J29

2.5-V CMOS

RGMII transmit data bus

14

ENETA_TX_D2

H29

2.5-V CMOS

RGMII transmit data bus

16

ENETA_TX_D3

H30

2.5-V CMOS

RGMII transmit data bus

9

ENETA_TX_EN

F30

2.5-V CMOS

RGMII transmit enable

55

ENETA_XTAL_25MHZ

—

2.5-V CMOS

25-MHz RGMII transmit clock

29

ENETA_MDI_P0

—

2.5-V CMOS

Media dependent interface

31

ENETA_MDI_N0

—

2.5-V CMOS

Media dependent interface